Abbiamo considerato un decodificatore a stadio singolo (lineare): è il più veloce, ma la sua implementazione con una significativa larghezza della parola di input è difficile, poiché richiede l'uso di elementi logici con un numero elevato di input, che è accompagnato da un grande carico sulle sorgenti del segnale di ingresso. Tipicamente, i decodificatori monostadio vengono eseguiti per un piccolo numero di ingressi, determinato dalle capacità degli elementi della serie di microcircuiti applicati. Pertanto, spesso il numero di uscite del decoder non è sufficiente per selezionare importo richiesto dispositivi a microprocessore. Utilizzando due decoder con un ingresso di abilitazione E, è possibile realizzare un decoder con numero di uscite N = 2 n+1 (Fig. 2.11.3).

Riso. 2.11.3. Decoder 3x8 basato su due decoder 2x4

Sulla fig. 2.11.3 mostra uno schema di un decoder 3x8 combinato implementato su due decoder 2x4 completi. Pertanto, è possibile creare un decoder 4x16 da 2 decoder 3x8, ecc. L'ingresso di abilitazione E viene utilizzato come bit di indirizzo. Quando E = 0, il decoder superiore funziona, quando E = 1, il decoder inferiore funziona, mentre tutte le uscite del decoder superiore sono 0.

È ampiamente utilizzato anche il metodo a cascata (piramidale) di costruzione di decodificatori con un numero elevato di uscite su microcircuiti di decodifica con un numero inferiore di uscite (Fig. 2.11.4).

Per abilitare il funzionamento di uno dei decoder 3x8 (DC2, DC3, DC4, DC5), viene fornito un segnale di abilitazione o disabilitazione all'ingresso E di ciascun decoder dal decoder DC1 (primo stadio), che è controllato dai bit di indirizzo A3 , A4.

Riso. 2.11.4. Schema di inclusione a cascata (piramidale) dei decoder

I bit di indirizzo A0, A1, A2 vengono alimentati in parallelo ai decoder del 2° stadio. Il numero totale di bit di indirizzo è aumentato di 2 bit.

Codificatori. Gli encoder sono dispositivi progettati per convertire un codice unitario in binario. All'uscita dell'encoder compare un codice binario multibit corrispondente al numero decimale dell'ingresso a cui è applicato il livello logico attivo. I codificatori binari eseguono l'operazione inversa dei decodificatori.

L'encoder è talvolta chiamato "coder" (dall'inglese coder) e serve, ad esempio, per convertire i numeri decimali digitati sulla tastiera di una pulsantiera in numeri binari. Se il numero di ingressi è così grande che l'encoder utilizza tutte le possibili combinazioni di segnali di uscita, tale encoder viene definito completo. Il numero di ingressi e uscite in un encoder completo è correlato dalla relazione N = 2 n , dove N è il numero di ingressi, n è il numero di uscite. Quindi, per convertire il codice della tastiera in un numero binario di quattro cifre, è sufficiente utilizzare solo 10 ingressi, mentre il numero totale di ingressi possibili sarà 16 (n = 2 4 = 16), quindi l'encoder 10x4 sarà incompleto .

Considera un esempio di costruzione di un codificatore per convertire un codice unitario a dieci bit (numeri decimali da 0 a 9) in un codice binario. In questo caso si assume che il segnale corrispondente ad un'unità logica sia applicato ad un solo ingresso per volta.

La tabella di verità per il codificatore è riportata nella Tabella 2.11.3.

Usando questo tavolo, scriviamo espressioni logiche per le variabili di output, includendo nella somma logica quelle variabili di input che corrispondono all'unità della corrispondente variabile di output.

Tavola di verità per il decodificatore

Tabella 2.11.3.

| Ingressi | esce | |||||||||||||

| № | X0 | X1 | X2 | X3 | X4 | X5 | X6 | X7 | X8 | X9 | A3 | A2 | A1 | A0 |

Scriviamo le equazioni logiche per le variabili di uscita A0, A1, A2, A3:

A0 = X1 v X3 v X5 v X7 v X9

A1 = X2 contro X3 contro X6 contro X7

A2 = X4 contro X5 contro X6 contro X7

Per un tale encoder, è facile costruire un circuito su elementi logici "OR" (Fig. 2.11.5).

Riso. 2.11.5. Schema di un codificatore incompleto 10x4

Istruzioni metodologiche per l'esecuzione del lavoro:

Annota nel rapporto, come al solito, il nome dell'opera, lo scopo dell'opera. Dare la definizione di decodificatore. Crea una tabella di verità per un decoder che ha 3 ingressi di indirizzo. Annotare le equazioni per ognuna delle 8 uscite del decoder. Costruisci un diagramma. Costruisci un circuito che implementa le funzioni del decoder in Multisim. Esplora il suo lavoro.

Esplora il funzionamento del chip di decodifica 2x4. Assemblare il circuito decoder mostrato in fig. 2.11.4 utilizzando solo decoder 2x4.

Ottieni diagrammi di temporizzazione del funzionamento del circuito. Per visualizzare tutti i segnali di ingresso e uscita del decoder, utilizzare 2 analizzatori.

Disegna un diagramma e spiega come funziona nel rapporto. Si prega di fornire diagrammi di temporizzazione. I diagrammi temporali devono essere mostrati su una pagina; i diagrammi relativi al tempo non possono essere continuati su un'altra pagina. Tutte le connessioni tra i segnali dovrebbero essere chiare.

Crea una tabella di verità per il codificatore 8x3 completo. Scrivere le funzioni logiche delle variabili di output. Costruisci e ricerca il circuito scrambler. Nella relazione, fornire una tavola di verità, equazioni, un diagramma costruito secondo equazioni, diagrammi di temporizzazione.

Annota le conclusioni corrispondenti a ciascun elemento del lavoro svolto.

Domande da preparare per il rapporto:

1. Definire un decodificatore.

2. Definire uno scrambler.

3. Cosa si intende per codice unitario?

4. Qual è la differenza tra un decoder completo e uno incompleto?

5. Qual è la differenza tra un codificatore completo e uno incompleto?

6. Qual è la differenza tra un decoder lineare e uno piramidale?

7. Un decoder lineare o piramidale ha più velocità?

8. Sono necessari maggiori costi hardware per implementare un decoder lineare o piramidale?

9. Perché i decodificatori e gli encoder vengono utilizzati nell'informatica?

12. Lavoro di laboratorio №12

Ricerca di multiplexer e demultiplexer

Obiettivo del lavoro: Studiare i principi di sintesi e funzionamento di multiplexer e demultiplexer.

Esercizio: Sintetizza il circuito multiplexer, studia il funzionamento del circuito. Esplora il chip multiplexer, costruisci e studia il funzionamento del circuito piramidale. Sintetizza il circuito demultiplexer, studia il funzionamento del circuito. Ricerca lavoro congiunto multiplexer e demultiplexer.

Introduzione teorica

Multiplexerè chiamato un dispositivo logico combinatorio progettato per la trasmissione controllata di dati da diverse fonti di informazioni in un canale di uscita. Gli ingressi del multiplexer sono divisi in informazioni D 0 , D 1 , ...... e controllo (indirizzo) UN 0 , UN 1 , …, UN n-1.

Il codice applicato agli input dell'indirizzo determina quale delle informazioni viene immessa questo momento passato all'uscita del circuito. Perché il N-bit codice binario può assumere 2 n valori, quindi se il numero di ingressi di indirizzo del multiplexer è N, il numero dei suoi input di informazioni deve essere uguale a 2 n .

Costruiamo una tabella di verità che mostri il funzionamento di un multiplexer con due input di indirizzo in base alla definizione. Indichiamo nella tabella A0 e A1 - indirizzi di input. D0, D1, D2, D3 - ingressi di 4 flussi di dati, quando si imposta l'indirizzo, i dati corrispondenti verranno trasmessi all'unica uscita del multiplexer Y (tabella 2.12.1).

La tabella si presenta così:

Tabella 2.12. 1

| Indirizzo | Dati | Uscita | ||||

| A1 | A0 | D0 | D1 | D2 | D3 | Y |

| D0 | D1 | D2 | D3 | D0 | ||

| D0 | D1 | D2 | D3 | D1 | ||

| D0 | D1 | D2 | D3 | D2 | ||

| D0 | D1 | D2 | D3 | D3 |

Scriviamo l'equazione per la funzione Y:

Y = LA1*LA0*RE0 v LA1*LA0 RE1 v LA1 LA0*RE2 v LA1 LA0 RE3.

Il circuito che implementa la funzione Y può essere realizzato su 2 inverter, 4 elementi "AND" a tre ingressi ed un elemento "OR" a quattro ingressi (Fig. 12.2.1).

Riso. 12.2.1. Circuito multiplexer 4-1

È possibile assemblare un decoder per implementare lo stesso circuito e usarlo per commutare gli ingressi sull'uscita Y (Fig. 2.12.2).

Riso. 2.12.2. Circuito multiplexer e suo simbolo

Nei casi in cui la funzionalità dei circuiti integrati multiplexer non soddisfa gli sviluppatori in termini di numero di input di informazioni, ricorrono al loro collegamento in cascata per aumentare il numero di input al valore richiesto. Maggior parte modo universale aumentare la dimensione del multiplexer consiste nel costruire una struttura piramidale composta da più multiplexer. In questo caso, il primo livello del circuito è una colonna contenente tanti multiplexer quanti sono necessari per ottenere il numero richiesto di ingressi di informazioni. Tutti i multiplexer in questa colonna sono commutati dallo stesso codice di indirizzo, composto dal numero corrispondente di cifre meno significative del codice di indirizzo comune. Le cifre superiori del codice di indirizzo sono utilizzate nel secondo livello, il cui multiplexer assicura il funzionamento alternativo dei multiplexer di primo livello verso un'uscita comune. Il circuito in cascata del multiplexer "16-1", realizzato sui multiplexer "4-1", è mostrato in fig. 2.12.3.

Riso. 2.12.3. Multiplexer in cascata 16-1

Un'applicazione tipica di un multiplexer è la trasmissione di informazioni da diverse sorgenti di informazioni (sensori) spazialmente separate all'ingresso di un ricevitore.

Supponiamo che la temperatura sia misurata ambiente in più stanze e i risultati di queste misurazioni devono essere inseriti in un dispositivo di registrazione, come un computer. Allo stesso tempo, poiché la temperatura cambia lentamente, non è necessario misurarla costantemente per ottenere una precisione sufficiente. È sufficiente disporre di informazioni a determinati intervalli fissi.

Il multiplexer svolge la funzione di collegare varie fonti di informazioni a un ricevitore a un dato comando.

Il multiplexer può essere utilizzato come elemento logico universale per implementare qualsiasi funzione logica dal numero di argomenti pari al numero di ingressi di indirizzo del multiplexer. Mostriamolo con l'esempio di una funzione logica data da tavola della verità(Tabella 2.12.2).

Tabella 2.12.2

| № | A2 | A1 | A0 | Y | № | A2 | A1 | A0 | Y |

Schema che implementa questa funzione mostrato in fig. 2.12.4.

Riso. 2.12.4. Implementazione di un circuito combinatorio mediante multiplexer

Demultiplatore- questo è un circuito combinatorio con un ingresso informazioni (D), n ingressi di controllo (indirizzo) (A0, A1, ..., An-1) e N = 2 n uscite (Y0, Y1, ..., YN- 1). Il codice binario che arriva agli ingressi indirizzo determina una delle N uscite, a cui viene trasmesso il valore della variabile proveniente dall'ingresso informazioni D. Il demultiplatore implementa una funzione inversa alla funzione multiplatore. È progettato per suddividere il flusso di dati di una fonte di informazioni in diversi canali di output.

Di seguito viene presentata la tabella di funzionamento del demultiplatore (Tabella 2.12.2), che dispone di 4 uscite informative (Y0, Y1, Y2, Y3) e n = 2 ingressi indirizzo (A0, A1).

Tabella 2.12.2

| Inserimento informazioni | Indirizzo | Punti di informazione | ||||

| D | A1 | A0 | Y0 | Y1 | Y2 | Y3 |

| D | D | |||||

| D | D | |||||

| D | D | |||||

| D | D |

Equazioni che descrivono il funzionamento del demultiplatore:

Y0 = RE LA1* LA0*; Y1 = RE LA1*LA0; Y2 = LA1 LA0*; Y3 = LA1 LA0.

Lo schema del demoltiplicatore costruito secondo queste equazioni e la sua rappresentazione grafica sono riportati in fig. 2.12.5.

Riso. 2.12.5. Schema del demultiplexer "1-4" e sua immagine condizionale

La funzione del demultiplexer è facilmente implementata utilizzando il decoder, se il suo ingresso "Abilita" - E viene utilizzato come ingresso informazioni del demultiplexer e gli ingressi 1, 2, 4 ... - come ingressi indirizzo del demultiplexer A0 , A1, A2, ... Infatti, con il valore attivo del segnale all'ingresso E, viene selezionata l'uscita corrispondente al codice applicato agli ingressi indirizzo. Pertanto, i circuiti integrati di decodificatori con un ingresso di abilitazione sono talvolta chiamati non solo decodificatori, ma decodificatori-demultiplatori.

Il termine "multiplexing" si riferisce al processo di trasmissione di dati da più fonti su un canale comune. Un multiplexer viene utilizzato come dispositivo che esegue l'operazione di riduzione dei dati in un canale sul lato di trasmissione. Tale dispositivo è in grado di separare temporalmente i segnali provenienti da più sorgenti e di trasmetterli al canale di comunicazione (linea) uno dopo l'altro in funzione del cambio di codici ai suoi ingressi di indirizzo.

Sul lato ricevente, di solito è necessario eseguire l'operazione inversa: demultiplexing, ad es. distribuzione di porzioni di dati ricevuti sul canale di comunicazione in momenti successivi, in base ai loro destinatari. Questa operazione viene eseguita dal demultiplatore. Condivisione multiplexer e demultiplexer per trasferire dati da 4 fonti a

4 ricevitori su una linea comune è illustrato in fig. 2.12.6.

Riso. 2.12.6. Condivisione multiplexer e demultiplexer per trasmissione dati

Informazioni simili.

I titolari del brevetto RU 2559705:

L'invenzione si riferisce al campo della tecnologia informatica, dell'automazione e può essere utilizzata in varie strutture e sistemi digitali controllo automatico, trasferimento di informazioni, ecc.

In vari sistemi di calcolo e controllo, i decodificatori sono ampiamente utilizzati, implementati sulla base della logica accoppiata transistor-transistor ed emettitore, operando secondo le leggi dell'algebra booleana e avendo due stati logici "0" e "1" in uscita, caratterizzato da bassi e alti potenziali. L'architettura classica del decoder è stata pubblicata in articoli e libri, i microchip vengono prodotti in serie.

Uno svantaggio significativo di questa classe di decodificatori è che i suoi elementi logici, utilizzando potenziali segnali binari, hanno una struttura a più livelli impossibile o inefficiente da utilizzare nei moderni processi tecnici a bassa tensione, nonché la non linearità delle modalità operative di gli elementi e la criticità dei parametri della struttura degli elementi logici e dei segnali di ingresso. In definitiva, ciò porta ad una diminuzione delle prestazioni dei decodificatori noti.

Come dispositivi di elaborazione informazioni digitali vengono utilizzate anche cascate di transistor per la conversione delle variabili logiche di ingresso (correnti), realizzate sulla base di specchi di corrente che implementano la funzione di elaborazione logica delle variabili di corrente di ingresso.

Un notevole inconveniente dei circuiti noti di questa classe è che non implementano la funzione di convertire due segnali di corrente in ingresso aventi quattro stati "00", "01", "10", "11" in quattro segnali di corrente in uscita. Ciò non consente di creare sulla sua base una base completa di strumenti di elaborazione del segnale con variabili correnti operanti sui principi dell'algebra lineare.

Nelle opere, così come nelle monografie del coautore di questa applicazione, è dimostrato che l'algebra booleana è un caso speciale di un'algebra lineare più generale, la cui implementazione pratica nella struttura dell'informatica e dei dispositivi logici di un nuovo la generazione dell'automazione richiede la creazione di un elemento base speciale, implementato sulla base della logica con segnali di rappresentazione interna a due valori e multivalore, in cui l'equivalente del segnale logico standard è il quanto corrente Ι 0 . Il dispositivo rivendicato "Decoder da 2 a 4" si riferisce a questo tipo di dispositivi logici e lavora con segnali di corrente in ingresso e genera un segnale di corrente in uscita.

Il prototipo più vicino del dispositivo rivendicato è il dispositivo logico "Decoder 2 to 4", presentato nel brevetto US 5742154, contenente il primo 1 e il secondo 2 ingressi logici del dispositivo, il primo 3, il secondo 4, il terzo 5, il quarto 6 uscite logiche di corrente del dispositivo, il primo 7, il secondo 8 e il terzo 9 transistor di uscita, le cui basi sono combinate e collegate alla prima 10 sorgente di tensione di polarizzazione, il quarto 11, il quinto 12 e il sesto 13 transistor di uscita di un diverso tipo di conduttività, le cui basi sono combinate e collegate alla seconda sorgente di tensione di polarizzazione 14, l'emettitore del primo transistor di uscita 7 collegato all'emettitore del quarto transistor di uscita 11, l'emettitore del secondo transistor di uscita 8 è collegato all'emettitore del quinto transistor a 12 uscite, l'emettitore del terzo transistor a 9 uscite è collegato all'emettitore del sesto transistor a 13 uscite, la prima uscita logica a 3 correnti del dispositivo è collegata al collettore delle prime 7 uscite transistor, i secondi 4 dispositivi di uscita logica corrente a è collegato al collettore del terzo transistor a 9 uscite, il collettore del quarto transistor a 11 uscite è collegato alla terza uscita logica a 5 correnti del dispositivo, il collettore del sesto transistor a 13 uscite è collegato alla quarta logica a 6 correnti uscita del dispositivo, il primo 15 e il secondo 16 mirror di corrente sono abbinati al primo 17 bus di alimentazione, il terzo 18 mirror di corrente, abbinato al secondo 19 bus di alimentazione, una sorgente di corrente di riferimento ausiliaria 20.

Lo scopo principale dell'invenzione proposta è quello di realizzare un elemento logico che preveda la decodifica dello stato di due variabili logiche di ingresso e la formazione di quattro segnali di uscita in forma corrente. In definitiva, ciò consente di aumentare la velocità dei dispositivi di conversione delle informazioni noti utilizzando il decodificatore dell'invenzione e creare una base di elementi di dispositivi di calcolo che operano sui principi dell'algebra lineare multivalore.

Il problema è risolto dal fatto che nel dispositivo logico "Decoder 2 to 4" (Fig. 1), contenente il primo 1 e il secondo 2 ingressi logici del dispositivo, il primo 3, il secondo 4, il terzo 5, il le quarte 6 uscite logiche di corrente del dispositivo, il primo 7, il secondo 8 e il terzo 9 transistor di uscita, le cui basi sono combinate e collegate alla prima 10 sorgente di tensione di polarizzazione, il quarto 11, il quinto 12 e il sesto 13 transistor di uscita di un diverso tipo di conduttività, le cui basi sono combinate e collegate alla seconda sorgente di tensione di polarizzazione 14, l'emettitore del primo transistor di uscita 7 è collegato all'emettitore del quarto transistor di uscita AND, l'emettitore del secondo transistor di uscita 8 è collegato all'emettitore del quinto transistor a 12 uscite, l'emettitore del terzo transistor a 9 uscite è collegato all'emettitore del sesto transistor a 13 uscite, la prima uscita logica a 3 correnti del dispositivo è collegata al collettore delle prime 7 uscite transistor, la seconda uscita logica a 4 correnti del dispositivo è collegata al collettore della terza uscita a 9 circa il transistor, il collettore del quarto transistor di uscita 11 è collegato alla terza uscita logica di corrente 5 del dispositivo, il collettore del sesto transistor di uscita 13 è collegato alla quarta uscita logica di corrente 6 del dispositivo, il primo 15 e secondo 16 mirror di corrente abbinati al primo bus di alimentazione 17, terzo mirror di corrente 18, abbinato al secondo bus di alimentazione 19, sorgente di corrente di riferimento ausiliaria 20, vengono forniti nuovi elementi e connessioni - il primo 1 ingresso logico del dispositivo è collegato all'ingresso del terzo specchio di corrente 18, il secondo ingresso logico 2 del dispositivo è collegato all'ingresso del primo specchio di corrente 15, il primo 21 l'uscita di corrente del primo specchio di corrente 15 è collegato agli emettitori combinati di il secondo 8 e il quinto 12 transistor di uscita e attraverso la sorgente di corrente di riferimento ausiliaria 20 è collegato al secondo 19 bus di alimentazione, la seconda 22 uscita di corrente del primo 15 specchio di corrente è collegata agli emettitori combinati del primo 7 e del quarto 11 transistor di uscita ov ed è collegato alla prima uscita di corrente 23 del terzo specchio di corrente 18, il collettore del secondo transistor di uscita 8 è collegato all'ingresso del secondo specchio di corrente 16, la cui uscita di corrente è collegata agli emettitori combinati del terzo 9 e sesto 13 transistor di uscita ed è collegato alla seconda uscita di corrente 24 dei terzi 18 specchi di corrente, e il collettore del quinto transistor di uscita 12 è collegato al secondo bus 19 della sorgente di alimentazione.

La disposizione dell'unità logica prototipo è mostrata in FIG. 1. Nella fig. 2 mostra uno schema del dispositivo rivendicato secondo il punto 1 delle rivendicazioni.

Nella FIG. 3 mostra uno schema del dispositivo rivendicato secondo il paragrafo 2, il paragrafo 3, il paragrafo 4 delle rivendicazioni.

Nella FIG. 4 è dato schema elettrico Fico. 3 nell'ambiente di simulazione al computer MS9 con l'implementazione specifica delle principali unità funzionali (specchi di corrente, sorgenti di corrente di riferimento).

Nella FIG. 5 presenta i risultati della simulazione al computer del circuito di FIG. 4.

Dispositivo logico "Decodificatore da 2 a 4" di Fig. 2 contiene il primo 1 e il secondo 2 ingressi logici del dispositivo, il primo 3, il secondo 4, il terzo 5, il quarto 6 uscite logiche di corrente del dispositivo, il primo 7, il secondo 8 e il terzo 9 transistor di uscita, le cui basi sono combinate e collegate al primo 10 generatore di tensione di polarizzazione, quarto 11, quinto 12 e sesto 13 transistor di uscita di diverso tipo di conduttività, le cui basi sono combinate e collegate al secondo 14 generatore di tensione di polarizzazione, il l'emettitore del primo transistor a 7 uscite è collegato all'emettitore del quarto transistor a 11 uscite, l'emettitore del secondo transistor a 8 uscite è collegato all'emettitore del quinto transistor a 12 uscite, l'emettitore del terzo transistor a 9 uscite è collegato a l'emettitore del sesto transistor a 13 uscite, la prima uscita logica a 3 correnti del dispositivo è collegata al collettore del primo transistor a 7 uscite, la seconda uscita logica a 4 correnti del dispositivo è collegata al collettore del terzo transistor a 9 uscite , il collettore del quarto transistore di uscita 11 è collegato al terzo 5 corrente lo uscita logica del dispositivo, il collettore del sesto transistor di uscita 13 è collegato alla quarta uscita logica di corrente 6 del dispositivo, il primo 15 e il secondo specchio di corrente 16 abbinato al primo bus di alimentazione 17, il terzo specchio di corrente 18 abbinato con il secondo bus di alimentazione 19, una corrente sorgente di riferimento ausiliaria 20. Il primo ingresso logico 1 del dispositivo è collegato all'ingresso del terzo specchio di corrente 18, il secondo ingresso logico 2 del dispositivo è collegato all'ingresso del primo specchio di corrente 15, la prima uscita di corrente 21 del primo specchio di corrente 15 è collegata agli emettitori combinati del secondo 8 e del quinto transistor di uscita 12 e attraverso la sorgente di corrente di riferimento ausiliaria 20 è collegata al secondo bus di alimentazione 19, il la seconda uscita di corrente 22 del primo specchio di corrente 15 è collegata agli emettitori combinati dei primi 7 e del quarto transistor di uscita 11 ed è collegata alla prima uscita di corrente 23 del terzo specchio di corrente 18, il collettore del secondo transistor di uscita 8 è collegato con l'ingresso l'alloggiamento del secondo specchio di corrente 16, la cui uscita di corrente è collegata agli emettitori combinati del terzo transistor di uscita 9 e sesto 13 ed è collegata alla seconda uscita di corrente 24 del terzo specchio di corrente 18, e il collettore del quinto transistor di uscita 12 è collegato al secondo bus di alimentazione 19.

Nella FIG. 3 in accordo con il paragrafo 2 delle rivendicazioni, il primo 1 ingresso logico del dispositivo è collegato all'ingresso del terzo 18 specchio di corrente tramite il primo stadio invertente aggiuntivo, realizzato nella forma del primo 26 specchio di corrente aggiuntivo, abbinato a i primi 17 bus di alimentazione.

Nella FIG. 3, in accordo con il paragrafo 3 delle rivendicazioni, il collettore del quarto transistore di uscita 11 è collegato alla terza uscita logica di corrente 5 del dispositivo attraverso il secondo stadio di inversione aggiuntivo, realizzato sotto forma di un secondo specchio di corrente aggiuntivo 27, abbinato al secondo bus di alimentazione 19.

Inoltre, nella fig. 3, in accordo con il paragrafo 4 delle rivendicazioni, il collettore del sesto transistore di uscita 13 è collegato alla quarta uscita logica di corrente 6 del dispositivo tramite un terzo stadio invertente aggiuntivo, realizzato sotto forma di un terzo specchio di corrente aggiuntivo 28, abbinato al secondo bus di alimentazione 19.

Si consideri il funzionamento del circuito di decodifica proposto con ingressi e uscite di corrente di Fig. 2.

Il decoder da 2 a 4 implementa funzioni ben note:

dove A 0 , A ¯ 0 - segnali diretti e inversi all'ingresso 1 del dispositivo di Fig. 2,

A 1 , A ¯ 1 - segnali diretti e inversi all'ingresso 2 del dispositivo di Fig. 2.

Una caratteristica della loro implementazione in algebra lineare è l'uso dell'operazione di differenza troncata per questo scopo:

la cui tavola di verità è riportata di seguito

Dalla tabella risulta che su quattro possibili combinazioni di valori delle variabili di input, un singolo valore della funzione corrisponde ad una sola combinazione corrispondente alla condizione A 0 >A 1 . Specificando le variabili di input dirette e inverse nella tabella di verità, è possibile ottenere un singolo valore della funzione corrispondente a una qualsiasi delle possibili combinazioni di valori delle variabili di input.

Applicando questa operazione si ottiene la seguente rappresentazione delle funzioni logiche del decoder:

L'implementazione di queste operazioni è la seguente.

I segnali delle variabili di ingresso A 0 e A 1 attraverso gli ingressi logici 1 e 2 vengono inviati al primo 15 e al terzo 18 specchio di corrente, attraverso i quali i segnali specificati vengono moltiplicati e il loro segno cambia. In questo caso, il segnale A 0 viene trasmesso sotto forma di corrente uscente (cioè sotto forma di A 0) e, utilizzando il terzo specchio di corrente 18, viene convertito in una corrente entrante (cioè nella forma -A 0), e A 1 arriva in forma diretta sotto forma di una corrente in entrata (cioè, sotto forma di -A 1) e con l'aiuto del primo specchio di corrente 15 viene convertito in una corrente in uscita (cioè, nella forma di A1).

Nel punto di connessione delle uscite 22 del primo specchio di corrente 15 e 23 del terzo specchio di corrente 18, viene implementata l'operazione A 1 -A 0. Il segnale differenza viene applicato agli emettitori combinati dei transistor 7 e 11, le cui modalità operative sono impostate dalle prime 10 e dalle seconde 14 sorgenti di tensione di polarizzazione.

Se il segnale di differenza è positivo, ad es. A 0 -A 1 >0, il transistor 7 è chiuso e il transistor 11 è aperto e all'uscita 5 viene fornito un quanto della corrente in ingresso corrispondente a -(A 0 -A 1)=A 1 -A 0 che implementa l'espressione (2). Per qualsiasi altra combinazione di valori quantici di corrente, non ci sarà corrente all'uscita 5.

Se A 0 -A 1 ≤0, allora il transistor 7 è aperto, e il transistor 11 è chiuso e l'uscita 3 riceve un quanto della corrente uscente corrispondente ad A 0 -A 1 che implementa l'espressione (3). Per qualsiasi altra combinazione di valori quantici correnti, non ci sarà corrente all'uscita 3.

Nel punto di connessione dell'uscita 21 del primo specchio di corrente e della sorgente di corrente di riferimento ausiliaria 20, A 1 -1 viene sottratto. Il segnale differenza viene applicato agli emettitori combinati dei transistor 8 e 12, le cui modalità operative sono impostate dalle prime 10 e dalle seconde 14 sorgenti di tensione di polarizzazione. Se il segnale di differenza è positivo, ad es. A 1 -1>0, il transistor 8 è chiuso e il transistor 12 è aperto. Se il segnale di differenza è minore o uguale a zero, allora il transistor 8 è aperto e il transistor 12 è chiuso.

Nel primo caso, il segnale attraverso il transistor 12 si chiude a massa. Nel secondo caso, il quanto della corrente differenziale in uscita A 1 -1 con l'aiuto del terzo specchio di corrente 16 viene convertito nel quanto della corrente in uscita 1-A 1 e il quanto della corrente in entrata -A 0 viene sottratto da esso. Il segnale differenza viene applicato agli emettitori combinati dei transistor 9 e 13, le cui modalità di funzionamento sono impostate dalle prime 10 e dalle seconde 14 sorgenti di tensione di polarizzazione. Se il segnale di differenza è positivo, ad es. il transistor 9 è chiuso e il transistor 13 è aperto. Allo stesso tempo, un segnale di differenza (1-A 1)-A 0 viene inviato all'uscita 6 sotto forma di quanto di corrente in uscita, che implementa l'espressione (4). Per qualsiasi altra combinazione di valori quantici di corrente, non ci sarà corrente all'uscita 4.

specificità questo dispositivoè la rappresentazione dei segnali di uscita sotto forma di quanti della corrente entrante (alle uscite 3 e 4) e uscente (alle uscite 5 e 6). Per il caso in cui sono necessari tutti i segnali di uscita nella stessa direzione, il circuito decodificatore mostrato in FIG. 3. La sua differenza dal diagramma in FIG. 2 è l'utilizzo di due ulteriori specchi di corrente 27 e 28, agli ingressi dei quali sono collegati i collettori dei transistori 11 e 13, e le uscite sono le uscite 5 e 6 del decodificatore. Di conseguenza, tutti i segnali di uscita sono rappresentati da quanti della corrente in ingresso.

Come si può vedere dalla descrizione di cui sopra, l'implementazione del dispositivo "Decoder 2 to 4" viene eseguita sotto forma di funzioni logiche standard secondo le leggi dell'algebra lineare formando la differenza dei quanti di corrente 10. L'implementazione di elementi sugli specchi di corrente consente in molti casi di ridurre la tensione di alimentazione e poiché tutti gli elementi dei circuiti ridotti funzionano in modalità attiva, che presuppone l'assenza di saturazione durante la commutazione, le prestazioni complessive del dispositivo aumentano. L'uso di valori stabili della corrente quanti I 0 , nonché la determinazione del segnale di uscita dalla differenza di queste correnti, garantisce una piccola dipendenza del funzionamento del circuito da fattori destabilizzanti esterni (deviazione della tensione di alimentazione, effetti di radiazione e temperatura, rumore di modo comune, ecc.).

Mostrato in FIG. 9, fig. 10 risultati di simulazione confermano le proprietà specificate dei circuiti proposti.

Pertanto, le soluzioni circuitali considerate del dispositivo logico "Decoder 2 to 4" sono caratterizzate da una rappresentazione di corrente binaria del segnale e possono essere utilizzate come base per dispositivi di calcolo e controllo che utilizzano l'algebra lineare, un caso speciale del quale è l'algebra booleana .

BIBLIOGRAFIA

1. Brevetto US 6243319 B1, fig. 13.

2. Brevetto US 5604712 A.

3. Brevetto US 4514829 A.

4. Brevetto USA 20120020179 A1.

5. Brevetto US 6920078 B2.

6. Brevetto US 6324117 B1, fig. 3.

7. Domanda di brevetto US 20040018019 A1.

8. Brevetto US 5568061 A.

9. Brevetto US 5148480 A, fig. 4.

10. Brzozowski I., Zachara L., Kos A. Universal design method of n-to-2n decoders // Mixed Design of Integrated Circuits and Systems (MIXDES), 2013 Atti della 20th International Conference, 2013. - P. 279 -284 fig. 1.

11. Subramanyam M.V. Switching Theory and Logic Design / Firewall Media, 2011. Secondo, - 783 c, fig. 3.174.

12. SN74LVC1G139 Decodificatore da 2 a 4 linee [ Risorsa elettronica]. URL: http://www.ti.com/lit/ds/symlink/sn741vc1g139.pdf.

13. Brevetto US 8159304, fig. 5.

14. Brevetto USA n. 5977829, fig. 1.

15. Brevetto USA n. 5789982, fig. 2.

16. Brevetto USA n. 5140282.

17. Brevetto USA n. 6624701, fig. 4.

18. Brevetto USA n. 6529078.

19. Brevetto USA n. 5734294.

20. Brevetto USA n. 5557220.

21. Brevetto USA n. 6624701.

22. Brevetto RU n. 2319296.

23. Brevetto RU n. 2436224.

24. Brevetto RU n. 2319296.

25. Brevetto RU n. 2321157.

26. Brevetto US 6556075, fig. 2.

27. Brevetto US 6556075, fig. 6.

28. Chernov N.I., Yugai V.Y., Prokopenko N.N., e altri Concetto di base della sintesi lineare di strutture digitali multivalore in spazi lineari // 11° Simposio di progettazione e test est-ovest (EWDTS 2013). - Rostov sul Don, 2013. - C. 146-149.

29. Malyugin V.D. Realizzazione di funzioni booleane mediante polinomi aritmetici // Automazione e telemeccanica, 1982. N. 4. pp. 84-93.

30. Chernov N.I. Fondamenti della teoria della sintesi logica delle strutture digitali nel campo dei numeri reali // Monografia. - Taganrog: TRTU, 2001. - 147 p.

31. Chernov N.I. Sintesi lineare delle strutture digitali ASOIU // Esercitazione. - Taganrog: TRTU, 2004 - 118 p.

1. Decoder da 2 a 4, contenente il primo (1) e il secondo (2) ingresso logico del dispositivo, la prima (3), la seconda (4), la terza (5), la quarta (6) uscita logica in corrente del dispositivo , il primo (7), il secondo (8) e il terzo (9) transistor di uscita, le cui basi sono combinate e collegate alla prima (10) sorgente di tensione di polarizzazione, il quarto (11), il quinto (12) e il sesto (13) transistor di uscita di diverso tipo di conduttività, le cui basi sono combinate e collegate alla seconda (14) sorgente di tensione di polarizzazione, l'emettitore del primo (7) transistor di uscita è collegato all'emettitore del quarto (11) ) transistor di uscita, l'emettitore del secondo (8) transistor di uscita è collegato all'emettitore del quinto (12) transistor di uscita, l'emettitore del terzo (9) transistor di uscita è collegato all'emettitore del sesto (13) transistor di uscita transistor di uscita, la prima (3) uscita logica di corrente del dispositivo è collegata al collettore del primo (7) transistor di uscita, la seconda (4) uscita logica di corrente del dispositivo è collegata al collettore del terzo (9) transistor di uscita transistor di uscita, colle Il fattore del quarto (11) transistor di uscita è collegato alla terza (5) uscita logica di corrente del dispositivo, il collettore del sesto (13) transistor di uscita è collegato alla quarta (6) uscita logica di corrente del dispositivo, il primo (15) e il secondo (16) mirror di corrente sono abbinati al primo (17) bus di alimentazione, il terzo (18) mirror di corrente è abbinato al secondo (19) bus di alimentazione, la sorgente di corrente di riferimento ausiliaria (20) , caratterizzato dal fatto che il primo (1) ingresso logico del dispositivo è collegato all'ingresso del terzo (18) mirror di corrente, il secondo (2) ingresso logico del dispositivo è collegato all'ingresso del primo (15) mirror di corrente specchio, la prima (21) uscita di corrente del primo (15) specchio di corrente è collegata agli emettitori combinati del secondo (8) e del quinto (12) transistor di uscita e attraverso la sorgente di corrente di riferimento ausiliaria (20) è collegata allo secondo (19) bus di alimentazione, la seconda (22) uscita di corrente del primo (15) specchio di corrente è collegata agli emettitori combinati della prima (7) e della quarta (11) uscita transistor ed è collegato alla prima (23) uscita di corrente del terzo (18) specchio di corrente, il collettore del secondo (8) transistor di uscita è collegato all'ingresso del secondo (16) specchio di corrente, la cui uscita di corrente è collegato agli emettitori combinati del terzo (9) e del sesto (13) transistor di uscita ed è collegato alla seconda (24) uscita di corrente del terzo (18) specchio di corrente e al collettore del quinto (12) transistor di uscita è collegato al secondo (19) bus di alimentazione.

2. Decodificatore da 2 a 4 secondo la rivendicazione 1, caratterizzato dal fatto che il primo (1) ingresso logico del dispositivo è collegato all'ingresso del terzo (18) specchio di corrente tramite il primo stadio invertente aggiuntivo, realizzato sotto forma del primo (26) mirror di corrente aggiuntivo, coerente con il primo (17) rail di alimentazione.

3. Decodificatore da 2 a 4 secondo la rivendicazione 1, caratterizzato dal fatto che il collettore del quarto (11) transistore di uscita è collegato alla terza (5) uscita logica in corrente del dispositivo tramite un secondo stadio invertente aggiuntivo, realizzato sotto forma di un secondo (27) specchio di corrente aggiuntivo, abbinato al secondo (19) binario di alimentazione.

4. Decodificatore da 2 a 4 secondo la rivendicazione 1, caratterizzato dal fatto che il collettore del sesto (13) transistore di uscita è collegato alla quarta (6) uscita logica in corrente del dispositivo tramite un terzo stadio invertente aggiuntivo, realizzato sotto forma di un terzo (28) specchio di corrente aggiuntivo, abbinato al secondo (19) binario di alimentazione.

Brevetti simili:

SOSTANZA: L'invenzione si riferisce a mezzi di codifica utilizzanti un codice a codice ridotto ad azzeramento adattativo. Il risultato tecnico consiste nel ridurre la quantità di informazioni trasmesse dal lato ricevente al lato trasmittente.

L'invenzione si riferisce alla tecnologia informatica, in particolare alla codifica di informazioni video. Il risultato tecnico consiste nell'aumentare l'efficienza di codifica e decodifica del bitstream di informazioni video suddividendo i dati in strati di entropia.

L'invenzione riguarda un metodo per codificare una sequenza di numeri interi, un dispositivo di memorizzazione e un segnale portante tale sequenza codificata, nonché un metodo per decodificare tale sequenza codificata.

L'invenzione riguarda un metodo di precodifica e un sistema e metodo per costruire un vocabolario di precodifica in un sistema MIMO (multiple input multiple output).

L'invenzione si riferisce al campo della tecnologia, che utilizza segnali digitalizzati, e può essere applicata in dispositivi di comunicazione, registrazione, registrazione, riproduzione, conversione, codifica e compressione di segnali, sistemi di controllo automatico.

L'invenzione si riferisce al campo delle telecomunicazioni, in particolare al campo dei dispositivi crittografici e dei metodi per la verifica di una firma digitale elettronica (EDS). .

L'invenzione si riferisce al campo dell'elaborazione di segnali digitali, in particolare alla compressione di dati e al miglioramento della codifica entropica di sequenze video. Il risultato tecnico è quello di aumentare l'efficienza e ridurre complessità computazionale codifica entropica. Un metodo per elaborare un flusso di dati costituito da una pluralità di elementi di sintassi si basa sulla sostituzione di elementi di sintassi i cui valori hanno un'alta probabilità di verificarsi con elementi di sintassi i cui valori hanno una bassa probabilità. Il contesto è determinato per l'elemento sintattico e viene calcolata la probabilità di occorrenza dei valori di quegli elementi sintattici nel modello di flusso di dati che hanno un determinato contesto. Sostituire elementi di sintassi flusso di dati avente un contesto specifico, se la probabilità calcolata dell'occorrenza del valore dell'elemento di sintassi è superiore a una determinata soglia, agli elementi di sintassi, i cui valori hanno una bassa probabilità. 3 n. e 10 zp f-ly, 4 ill., 2 tab.

L'invenzione si riferisce alla tecnologia della comunicazione ed è intesa per misurare lo spettro dei segnali acustici informativi. EFFETTO: miglioramento della precisione della misurazione dello spettro dei segnali acustici informativi, espansione funzionalità dispositivi mediante binding valori istantanei spettro a segmenti regolabili in lunghezza di un segnale acustico temporaneo. Per fare ciò, nel metodo di misurazione dello spettro viene utilizzata la trasformata coseno discreta (DCT) anziché la trasformata veloce di Fourier (FFT), che consente di aumentare la precisione della misurazione dello spettro dei segnali acustici aumentando la risoluzione, riducendo il livello dei lobi laterali della trasformazione della finestra nello spettro e riducendo l'oscillazione dei componenti della stima dell'ampiezza spettrale, e consente anche di ridurre la durata dei segmenti del segnale acustico, su cui viene misurato lo spettro istantaneo , pur formando invece di uno due segnali (principale e aggiuntivo), e il segnale acustico digitale aggiuntivo è ortogonale a quello principale, sono legati anche i valori istantanei misurati dello spettro, il modulo dello spettro e la frequenza di fase caratteristica del segnale a segmenti del segnale acustico temporale regolabili in termini di posizione temporale e durata, sui quali viene misurato tale spettro. 2 np f-ly, 8 ill.

L'invenzione riguarda comunicazone wireless. Il risultato tecnico è un aumento dell'immunità ai disturbi, dell'affidabilità e dell'efficienza della comunicazione, mentre il consumo energetico può essere ridotto. Per questo, il metodo prevede: la fase S1, in cui il dispositivo master genera un codice di sequenza tramite un apposito encoder, e trasmette il codice di sequenza a ciascun dispositivo slave in modo continuo per un periodo di tempo prestabilito secondo una richiesta di comunicazione, dove il l'encoder specifico è un registro a scorrimento con feedback eseguito su un particolare polinomio il cui ordine e coefficienti sono correlati alla richiesta di collegamento, mentre tutti i coefficienti e i valori iniziali non sono uguali a 0 contemporaneamente; determinato periodo un tempo maggiore o uguale alla somma del periodo di sonno e del periodo di rilevamento dello slave, che costituisce un ciclo di sonno e veglia; fase S2, in cui il dispositivo slave riceve una parte continua del codice di sequenza nel periodo di rilevamento, decodifica il codice di sequenza mediante un decodificatore corrispondente al codificatore ed esegue un'operazione appropriata in base al risultato della decodifica. 2 n. e 10 zp f-ly, 5 ill.

L'invenzione si riferisce alla tecnologia di comunicazione ed è destinata alla codifica e alla decodifica di segnali. Il risultato tecnico è un aumento della precisione dei segnali di codifica e decodifica. Il metodo di codifica del segnale include l'ottenimento di un segnale nel dominio della frequenza secondo un segnale di ingresso; allocare bit predeterminati al segnale nel dominio della frequenza secondo una regola di allocazione predeterminata; regolare l'allocazione di bit per il segnale nel dominio della frequenza quando la frequenza più alta del segnale nel dominio della frequenza a cui i bit sono allocati supera un valore predeterminato; e codificare il segnale nel dominio della frequenza secondo l'allocazione di bit per il segnale nel dominio della frequenza. 4 n. e 16 zp f-ly, 9 ill.

L'invenzione si riferisce al campo delle telecomunicazioni ed è destinata a proteggere le informazioni segrete trasmesse. Risultato tecnico - alto livello sicurezza delle informazioni crittografate. Un metodo per crittografare le informazioni, inclusa la costruzione di una tabella di corrispondenze di simboli e dei loro equivalenti nello spazio (00; FF) nel sistema esadecimale, generando una nuova tabella di corrispondenze modificando la tabella originale, spostando la tabella originale, ad es. la riga delle corrispondenze viene spostata del numero specificato di caratteri, la codifica delle informazioni originali e la sua compressione al volume desiderato utilizzando l'apposita tabella di codifica Unicode. 2 scheda.

L'invenzione si riferisce alla codifica/decodifica segnale digitale, costituito da blocchi consecutivi di campioni. Il risultato tecnico è quello di migliorare la qualità del suono codificato. La codifica comprende l'applicazione di una finestra di pesatura a due blocchi di M campioni consecutivi. In particolare, tale finestra di ponderazione è asimmetrica e contiene quattro sezioni separate, che proseguono sequenzialmente sui due blocchi sopra menzionati, con la prima sezione crescente durante il primo intervallo di tempo, la seconda sezione avente un valore di ponderazione costante durante il secondo intervallo di tempo, la terza sezione decrescente nel tempo, il terzo intervallo di tempo e la quarta sezione hanno un valore di ponderazione costante durante il quarto intervallo di tempo. 6 n. e 11 zp f-ly, 10 ill.

L'invenzione si riferisce al campo dell'elaborazione di segnali digitali, in particolare a metodi per la codifica/decodifica di immagini video digitali. Il risultato tecnico è quello di aumentare il rapporto di compressione delle immagini video con una leggera diminuzione della qualità dell'immagine decodificata rispetto alle immagini aventi una natura ad alta frequenza dello spettro del segnale. Viene proposto un metodo per codificare/decodificare immagini video digitali. Secondo il metodo, nel processo di codifica, un'ulteriore componente ad alta frequenza viene aggiunta riga per riga alla componente a bassa frequenza della trasformata wavelet per smussare la funzione originale, che viene utilizzata per la codifica, ma soppressa sul lato della decodifica da utilizzando un filtro passa-basso. Inoltre, la codifica viene implementata utilizzando un funzionale con due obiettivi: aumentare il rapporto di compressione dei dati e mantenere la qualità dell'immagine decodificata, e le caratteristiche del filtro di decodifica vengono prese in considerazione come limitazione della comunicazione in fase di codifica. 8 riproduz., 3 tab.

L'invenzione si riferisce al campo della tecnologia di comunicazione senza fili. EFFETTO: miglioramento della qualità della comunicazione sopprimendo l'interferenza sequenziale tra i flussi di segnale. Il metodo di precodifica include: eseguire la preelaborazione di precodifica su un segnale da trasmettere, la preelaborazione provocando un aumento di potenza del segnale da trasmettere; selezionare un algoritmo di limitazione della potenza secondo la regola di selezione; eseguire un'operazione di limitazione di potenza sul segnale preelaborato secondo l'algoritmo di limitazione di potenza selezionato; e generare un segnale precodificato secondo il segnale a potenza limitata. Una forma di realizzazione della presente invenzione descrive inoltre un trasmettitore, un ricevitore e un sistema di precodifica. Nella presente invenzione, l'effetto negativo esercitato dall'operazione di limitazione di potenza sulla trasmissione di segnali può essere ridotto il più possibile nel momento in cui la potenza di trasmissione è limitata utilizzando l'operazione di limitazione di potenza. 5 n. e 12 zp f-ly, 8 ill.

La presente invenzione si riferisce al campo della codifica e decodifica ed è destinata alla quantizzazione di vettori inviluppo di frequenza. EFFETTO: maggiore efficienza di quantizzazione dei vettori di inviluppo di frequenza. Il metodo include: dividere N inviluppi di frequenza in un frame in N1 vettori, dove ogni vettore nei vettori N1 include M inviluppi di frequenza; quantizzare il primo vettore in N1 vettori utilizzando il primo vocabolario per ottenere una parola di codice corrispondente al primo vettore quantizzato, dove detto primo vocabolario è suddiviso in sezioni 2B1; determinare, secondo la parola di codice corrispondente al primo vettore quantizzato, che il primo vettore quantizzato è associato alla sezione i-esima nelle sezioni 2B1 di detto primo vocabolario; determinare un secondo vocabolario secondo il vocabolario della sezione i-esima; e quantizzare il secondo vettore in N1 vettori basati su detto secondo vocabolario. Nelle forme di realizzazione della presente invenzione, gli inviluppi di frequenza sono divisi in più vettori con taglie più piccole, in modo che la quantizzazione vettoriale possa essere eseguita su vettori di inviluppo di frequenza utilizzando un codebook con meno bit. 2 n. e 6 zp f-ly, 3 ill.

Il gruppo delle invenzioni si riferisce al campo della codifica. Il risultato tecnico è quello di aumentare l'efficienza della compressione dei dati. Il metodo per codificare i dati di ingresso (D1) include la determinazione essenzialmente di blocchi di dati e/o pacchetti di dati ripetuti in almeno uno dei frammenti di dati di ingresso (D1), mentre i blocchi di dati e/o i pacchetti di dati includono un corrispondente insieme di elementi, dove gli elementi includono un insieme di bit determinare se gli elementi sono invariati all'interno di blocchi di dati e/o pacchetti di dati che si ripetono sostanzialmente, e/o determinare che gli elementi all'interno di blocchi di dati e/o pacchetti di dati che si ripetono sostanzialmente cambiano; codificare gli elementi invariati in dati codificati (E2) utilizzando almeno un simbolo corrispondente o almeno un bit corrispondente che indica nessuna variazione negli elementi invariati rispetto ai loro elementi corrispondenti nel blocco di dati di riferimento e/o nel pacchetto di dati; e codificare gli elementi modificati in dati codificati (E2). 6 n. e 28 zp f-ly, 8 ill.

L'invenzione si riferisce ai decodificatori. Il risultato tecnico consiste nell'aumentare la velocità dei dispositivi di conversione delle informazioni utilizzando il decodificatore secondo l'invenzione. Il primo ingresso logico del dispositivo è collegato all'ingresso del terzo specchio di corrente, il secondo ingresso logico del dispositivo è collegato all'ingresso del primo specchio di corrente, la prima uscita di corrente del primo specchio di corrente è collegata al combinato emettitori del secondo e quinto transistor di uscita ed è collegata al secondo bus di alimentazione tramite una sorgente di corrente di riferimento ausiliaria, la seconda uscita di corrente del primo specchio di corrente è collegata agli emettitori combinati del primo e quarto transistor di uscita ed è collegata a la prima uscita di corrente del terzo specchio di corrente, il collettore del secondo transistor di uscita è collegato all'ingresso del secondo specchio di corrente, la cui uscita di corrente è collegata agli emettitori combinati del terzo e del sesto transistor di uscita ed è collegata con la seconda uscita di corrente del terzo specchio di corrente e il collettore del quinto transistore di uscita sono collegati al secondo bus di alimentazione. 3 wp f-ly, 5 ill.

I decoder sono dispositivi funzionali digitali progettati per riconoscere i codici binari.

I decodificatori binari, essendo un convertitore di codice, converte un codice binario ad uso diretto in un codice "1 su N". In una tale combinazione di codice, solo un bit è occupato da un'unità e tutto il resto è zero. Tabella della verità per un decodificatore progettato per riconoscere un quattro bit codice binario viene presentata la tabella 2.1

Tabella 2.1

La tabella 1 mostra che, a seconda del codice binario in ingresso, solo una delle sue uscite è nello stato eccitato all'uscita del decodificatore. Dalla stessa tabella risulta che un decodificatore binario con n ingressi deve avere 2 n uscite corrispondenti al numero di combinazioni di codice di un codice binario a n bit. Tale decodificatore è chiamato completare

, A differenza di incompleto

, per cui parte delle combinazioni di codice di input non viene utilizzata e il numero di output per cui  meno di 2 n.

meno di 2 n.

Nel campo principale del simbolo del decoder (Fig. 2.5), sono apposte le lettere DC (dalla parola inglese Decoder). Gli ingressi del decodificatore sono generalmente indicati dai loro pesi binari. Oltre agli ingressi di informazione, il decodificatore ha solitamente uno o più ingressi di abilitazione lavoro, indicati come E (Enable). Se a questo ingresso è presente un segnale di abilitazione il decoder opera secondo la tabella di verità, in sua assenza tutte le uscite del decoder sono passive.

Il funzionamento del decoder è descritto da un sistema di espressioni booleane:

CON  la soluzione chimicotecnica dei decoder è mostrata in Fig. 2.6.

la soluzione chimicotecnica dei decoder è mostrata in Fig. 2.6.

Come si può vedere dalla figura. 2.6., il decoder è costituito da 2n inverter del codice di ingresso, che formano i valori diretti e inversi delle variabili del codice di ingresso, due inverter all'ingresso di permesso, e 2 n -1 congiuntori, che formano le uscite del circuito . La bassa capacità di bit dei decodificatori seriali solleva la questione dell'aumento della loro capacità di bit. Dai decodificatori a bit basso, puoi costruire un circuito equivalente a un decodificatore a bit grande. A tale scopo la parola di ingresso è suddivisa in campi, mentre la profondità di bit del campo delle cifre meno significative corrisponde alla larghezza di bit dei decoder disponibili. Il restante campo dei bit più significativi viene utilizzato per ottenere un segnale per abilitare il funzionamento di uno dei decoder che decodificano il campo dei bit meno significativi.

IN  come esempio in Fig. 2.7 mostra uno schema per decodificare un codice a cinque bit utilizzando i decodificatori "3-8" e "2-4". Per ottenere le 32 uscite richieste, una colonna del secondo livello viene compilata da quattro decodificatori "3-8" DC1-DC4. Il decoder "2-4" prende i due bit più significativi del codice in ingresso. L'uscita eccitata di questo decodificatore apre uno dei decodificatori di colonna all'ingresso di abilitazione, ed il decodificatore selezionato decodifica i bit meno significativi della parola d'ingresso. Ogni parola di ingresso corrisponde all'eccitazione di una delle uscite F 0 -F 31 . Ad esempio, quando si decodifica la parola x 4 x 3 x 2 x 1 x 0 =11001 2 =25 10, l'ingresso del decodificatore di primo livello ha il codice 11, che eccita il suo numero di uscita tre (contrassegnato da una croce), che consente il funzionamento del decoder DC4. L'ingresso DC4 è codificato 001, quindi la sua prima uscita sarà eccitata, cioè 25 uscita del circuito. L'autorizzazione o il divieto generale del funzionamento del circuito viene effettuato all'ingresso E del decoder del primo livello.

come esempio in Fig. 2.7 mostra uno schema per decodificare un codice a cinque bit utilizzando i decodificatori "3-8" e "2-4". Per ottenere le 32 uscite richieste, una colonna del secondo livello viene compilata da quattro decodificatori "3-8" DC1-DC4. Il decoder "2-4" prende i due bit più significativi del codice in ingresso. L'uscita eccitata di questo decodificatore apre uno dei decodificatori di colonna all'ingresso di abilitazione, ed il decodificatore selezionato decodifica i bit meno significativi della parola d'ingresso. Ogni parola di ingresso corrisponde all'eccitazione di una delle uscite F 0 -F 31 . Ad esempio, quando si decodifica la parola x 4 x 3 x 2 x 1 x 0 =11001 2 =25 10, l'ingresso del decodificatore di primo livello ha il codice 11, che eccita il suo numero di uscita tre (contrassegnato da una croce), che consente il funzionamento del decoder DC4. L'ingresso DC4 è codificato 001, quindi la sua prima uscita sarà eccitata, cioè 25 uscita del circuito. L'autorizzazione o il divieto generale del funzionamento del circuito viene effettuato all'ingresso E del decoder del primo livello.

Insieme all'uso dei decodificatori per lo scopo previsto, possono essere utilizzati per implementare funzioni logiche arbitrarie, poiché tutti i termini congiuntivi che possono essere composti da un dato numero di argomenti vengono generati alle uscite del decodificatore. Una funzione logica in SDNF è una disgiunzione di un certo numero di tali termini. Combinandoli secondo lo schema OR, puoi ottenere qualsiasi funzione di un dato numero di argomenti.

La Figura 2.8 mostra l'implementazione hardware della funzione sommatore modulo due come esempio.

Uno degli elementi molto importanti tecnologia digitale, e specialmente nei computer e nei sistemi di controllo sono codificatori e decodificatori.

Quando sentiamo la parola codificatore o decodificatore, ci vengono in mente frasi di film di spionaggio. Qualcosa del tipo: decifrare la spedizione e crittografare la risposta.

Non c'è niente di sbagliato in questo, dal momento che le macchine di crittografia della nostra residenza e di quelle straniere utilizzano codificatori e decodificatori.

Codificatori.

Pertanto, l'encoder (codificatore) è dispositivo elettronico, in questo caso, un microcircuito che converte il codice di un sistema numerico nel codice di un altro sistema. I più utilizzati in elettronica sono gli encoder che convertono un codice decimale posizionale in binario parallelo. In questo modo è possibile indicare l'encoder sullo schema elettrico.

Ad esempio, immaginiamo di tenere in mano una normale calcolatrice, che ora viene utilizzata da qualsiasi studente.

Poiché tutte le azioni nella calcolatrice vengono eseguite con numeri binari (ricorda le basi dell'elettronica digitale), dopo la tastiera c'è un codificatore che converte i numeri inseriti in forma binaria.

Tutti i pulsanti della calcolatrice sono collegati a un filo comune e, premendo ad esempio il pulsante 5 all'ingresso dell'encoder, otteniamo immediatamente in uscita la forma binaria di questo numero.

Naturalmente, il codificatore della calcolatrice ha Di più input, poiché oltre ai numeri, è necessario inserire altri simboli di operazioni aritmetiche, pertanto, non solo i numeri in forma binaria, ma anche i comandi vengono rimossi dalle uscite del codificatore.

Se consideriamo la struttura interna dell'encoder, è facile assicurarsi che sia realizzata sui più semplici elementi logici di base.

In tutti i dispositivi di controllo che operano su logica binaria, ma per comodità dell'operatore dispongono di una tastiera decimale, vengono utilizzati encoder.

Decoder.

I decoder appartengono allo stesso gruppo, solo che funzionano esattamente al contrario. Convertono il binario parallelo in decimale posizionale. La designazione grafica condizionale sul diagramma può essere la seguente.

O così.

Parlando in modo più completo dei decodificatori, vale la pena dire che possono convertire il codice binario in sistemi diversi calcolo (decimale, esadecimale, ecc.). Tutto dipende dallo scopo e dallo scopo specifici del microcircuito.

L'esempio più semplice. Hai visto più di una volta un indicatore digitale a sette segmenti, ad esempio un LED. Visualizza cifre decimali e numeri a cui siamo abituati fin dall'infanzia (1, 2, 3, 4...). Ma, come sai, l'elettronica digitale funziona con numeri binari, che sono una combinazione di 0 e 1. Cosa ha convertito il codice binario in decimale e ha inviato il risultato a un indicatore digitale a sette segmenti? Probabilmente hai già indovinato che l'ha fatto il decoder.

Il lavoro del decoder può essere valutato dal vivo se si assembla un semplice circuito costituito da un chip decoder K176ID2 e un indicatore LED a sette segmenti, chiamato anche "otto". Dai un'occhiata allo schema, è più facile capire come funziona il decoder. Una breadboard senza saldatura può essere utilizzata per assemblare rapidamente il circuito.

Per riferimento. Il microcircuito K176ID2 è stato sviluppato per controllare un indicatore LED a 7 segmenti. Questo chip è in grado di convertire il codice binario da 0000 Prima 1001 , che corrisponde alle cifre decimali da 0 a 9 (una decade). Il resto, le combinazioni più vecchie semplicemente non vengono visualizzate. Le conclusioni C, S, K sono ausiliarie.

Il chip K176ID2 ha quattro ingressi (1, 2, 4, 8). A volte vengono anche indicati RE0-RE3. A questi ingressi viene assegnato un codice binario parallelo (ad esempio, 0001). In questo caso, il codice binario ha 4 bit. Il microcircuito converte il codice in modo che le uscite ( a-g) compaiono i segnali, che formano cifre decimali e numeri a cui siamo abituati sull'indicatore a sette segmenti. Poiché il decoder K176ID2 è in grado di visualizzare cifre decimali nell'intervallo da 0 a 9, le vedremo solo sull'indicatore.

4 interruttori a levetta (S1 - S4) sono collegati agli ingressi del decoder K176ID2, con l'aiuto del quale è possibile applicare un codice binario parallelo al decoder. Ad esempio, quando si chiude l'interruttore a levetta S1 un'unità logica viene applicata alla 5a uscita del microcircuito. Se apri i contatti dell'interruttore a levetta S1- questo corrisponderà a uno zero logico. Con l'aiuto di interruttori a levetta, possiamo impostare manualmente la logica 1 o 0 agli ingressi del microcircuito, penso che tutto sia chiaro con questo.

Lo schema mostra come viene applicato il codice 0101 agli ingressi del decoder DD1. Indicatore LED verrà visualizzato il numero 5. Se solo l'interruttore a levetta S4 è chiuso, sull'indicatore verrà visualizzato il numero 8. Per scrivere un numero da 0 a 9 in codice binario, sono sufficienti quattro cifre: un 3 * 8 + un 2 * 4 + un 1 * 2 + un 0 * 1, Dove uno 0 - un 3, sono numeri del sistema numerico (0 o 1).

Rappresentiamo il numero 0101 in forma decimale 0101 = 0*8 + 1*4 + 0*2 + 1*1 = 4 + 1 = 5 . Ora diamo un'occhiata al diagramma e vediamo che il peso della cifra corrisponde al numero per il quale 0 o 1 viene moltiplicato nella formula.

Un decodificatore basato sulla tecnologia TTL - K155ID1 è stato utilizzato un tempo per controllare una scarica di gas indicatore digitale tipo IN8, IN12, molto richiesti negli anni '70, poiché gli indicatori LED a bassa tensione erano ancora molto rari.

Tutto è cambiato negli anni '80. Era possibile acquistare liberamente matrici LED a sette segmenti (indicatori) e tra i radioamatori si diffuse un boom nell'assemblaggio di orologi elettronici. Fatti in casa Orologio digitale non raccolto per la casa solo pigro.

Come notato nel paragrafo 3.2, i dispositivi digitali sono divisi in combinatori e sequenziali. I dispositivi di combinazione includono tali dispositivi digitali, i cui segnali di uscita dipendono solo dal valore corrente dei segnali di ingresso. Questi dispositivi, a differenza di quelli sequenziali, non hanno memoria. Dopo il completamento dei processi transitori in questi dispositivi, i valori di uscita vengono impostati alle loro uscite, che non sono influenzate dalla natura dei processi transitori.

Qualsiasi complesso dispositivo digitale può essere suddiviso in una parte combinatoria che esegue operazioni logiche ed elementi di memoria. In linea di principio, la parte combinatoria può essere eseguita su elementi logici, ma questo è troppo complicato e costoso. È molto più facile utilizzare dispositivi combinatori già pronti per questo. I principali dispositivi combinatori includono decodificatori, codificatori, multiplexer (distributori), demultiplexer e sommatori.

Decoder

Decodificatore (decoder ) – Si tratta di un dispositivo combinatorio che consente di riconoscere i numeri rappresentati da un codice posizionale a n bit. Se all'ingresso del decodificatore "-bit codice binario, allora alla sua uscita il codice "1 da Ν". Nella combinazione di codici di questo codice, solo una posizione è occupata da uno e tutto il resto è zero. Ad esempio, il codice "1 di Ν", contenente 4 combinazioni di codice sarà rappresentato come segue:

Tale codice è chiamato unitario pertanto, il decodificatore è un convertitore di un codice binario posizionale in uno unitario. Poiché il numero possibile di numeri codificati dal codice binario n bit è uguale al numero di insiemi di e argomenti (N= 2"), allora un decoder con n ingressi deve avere 2n uscite. Tale decodificatore è chiamato completo. Se parte dei set di input non viene utilizzata, il decodificatore viene definito incompleto e il suo numero di output è inferiore a 2n. Pertanto, a seconda del codice binario di ingresso, all'uscita del decodificatore viene eccitato solo uno dei circuiti di uscita, dal numero del quale è possibile riconoscere il numero di ingresso.

I decodificatori vengono utilizzati per decifrare gli indirizzi delle celle di memoria, visualizzare lettere e numeri su monitor, indicatori e altri dispositivi. Molto spesso sono incorporati in LSI, come, ad esempio, in dispositivi di memoria a semiconduttore, ma sono disponibili anche come circuiti integrati di livello medio di integrazione.

Illustriamo l'implementazione dei decodificatori utilizzando l'esempio di un decodificatore completo di numeri a tre cifre. La tabella di verità del decodificatore è presentata in Tabella. 3.5.

Tabella 3.5

|

X 3 |

X 2 |

X 1 |

si 0 |

si 1 |

si 2 |

si 3 |

si 4 |

si 5 |

si 6 |

si 7 |

|

Come puoi vedere, ogni uscita X i è uguale a uno su un solo set, quindi il funzionamento del decoder è descritto da otto funzioni - in base al numero di uscite del decoder, ciascuna delle quali è una congiunzione (AND logico) di tre argomenti:

Lo schema di un decodificatore completo a tre bit è mostrato in fig. 3.12. Per implementare una funzione si i, è necessario un congiuntore a tre ingressi. Poiché ci sono sia argomenti diretti che inversi agli ingressi dei congiuntori, sono necessari tre invertitori nel circuito del decodificatore (vedi Fig. 3.12, UN).

Riso. 3.12.

UN – schema logico; B – simbolo del decoder con ingressi di sincronizzazione e risoluzione

Spesso i decodificatori vengono eseguiti con sincronizzazione controllata, in cui la decrittazione del codice verrà eseguita durante la fornitura dell'impulso di clock ricevuto all'ingresso CON, solo a condizione che l'input IT è stato dato un unico segnale di consenso (vedi Fig. 3.12, B). Per implementare tale condizione sono necessari congiuntori a quattro ingressi, il quarto dei quali riceve un segnale di abilitazione. Questo segnale è generato da un connettore a due ingressi quando i segnali corrispondono CON E IT.

Il numero di contatti in un caso standard di un semplice IC è limitato (14, 16 o 24), quindi i decodificatori prodotti sotto forma di IC hanno una piccola dimensione del codice di input (tre, meno spesso quattro). Quindi, ad esempio, solo un decodificatore completo a tre bit può essere inserito in un pacchetto a 16 pin. Se è necessario creare un decoder di capacità maggiore, viene utilizzato un collegamento in cascata di decoder di capacità ridotta.

Esempio 3.1. Lascia che sia necessario creare un decodificatore a cinque bit basato su decodificatori a tre bit (Fig. 3.13).

Riso. 3.13.

Soluzione. Un decodificatore a cinque bit dovrebbe avere 25 = 32 uscite. Dividi le cinque cifre in quelle più giovani X 2, X 1, X 0 e precedenti X 4, X 3. Quindi i più giovani possono essere applicati agli ingressi di quattro decoder a 3 bit del secondo stadio e formare 8 4 = 32 uscite. Utilizzo degli ingressi di abilitazione ΕΝ, si può scegliere uno dei quattro decoder del secondo stadio, che dovrebbero formare un unico segnale. Per fare ciò forniremo i due bit superiori agli ingressi del decoder di controllo del primo stadio e collegheremo le sue uscite agli ingressi di abilitazione ΕΝ decodificatori del primo stadio.

Poniamo ad esempio che il codice in ingresso sia pari a 11011 = 2710. Poiché i bit più significativi sono "11", il decoder di controllo consentirà il funzionamento del 4° decoder del secondo stadio. In questo caso le uscite dei primi tre decoder saranno zero, e l'uscita "3" del quarto decoder, cioè F 27 sarà logico.

I decoder sono ampiamente utilizzati nei sistemi di controllo processi tecnologici. Molti attuatori, come un motore elettrico, un attuatore basato su elettromagnete, possono essere controllati con due soli comandi: "on" e "off". In questo caso è conveniente assegnare un "1" logico al comando "on" e un "1" logico al comando "off". Per controllare tali dispositivi vengono utilizzati codici unitari, in cui ogni cifra è rigidamente associata dispositivo specifico. Il numero di dispositivi controllati può essere di diverse decine e il decoder deve avere un numero adeguato di uscite.

Sulla fig. 3.14 mostra uno schema di controllo per otto attuatori basato su un decoder. Il circuito contiene otto circuiti simili che abilitano/disabilitano l'attuatore. Lo stato del dispositivo esecutivo è fissato da un elemento di memoria, che viene spesso utilizzato come trigger (vedi paragrafo 3.9). L'input in alto attiva l'elemento e quello in basso lo disattiva. Il segnale che determina lo stato acceso o spento viene inviato ai corrispondenti circuiti AND (superiori o inferiori) di tutti gli elementi di memoria, ma tale segnale viene percepito solo dall'elemento selezionato dal decoder. Per fare ciò, oltre ai segnali ON/OFF, viene fornito contemporaneamente al circuito di controllo un codice che entra nel decoder e determina il numero dell'attuatore. Il segnale dall'uscita dell'elemento di memoria viene amplificato ed entra nel circuito di commutazione dell'attuatore. Qui è possibile installare un optoisolatore di isolamento galvanico (vedi paragrafo 2.10), un relè elettromagnetico che fornisce un'elevata tensione di commutazione, ad esempio = 220 V, un avviatore elettromagnetico che fornisce una tensione trifase al motore elettrico.

Riso. 3.14.

Codificatori

codificatore – si tratta di un dispositivo combinatorio che svolge le funzioni inverse al decoder. Quando un segnale viene applicato ad uno dei suoi ingressi (codice unitario), in uscita deve essere formato il codice binario corrispondente.

Se il numero di ingressi all'encoder è 2n, allora il numero di uscite deve ovviamente essere uguale a P, quelli. il numero di bit binari che possono codificare situazioni da 2”.

Illustriamo la sintesi del circuito encoder per P = 3. La tavola di verità ha la forma mostrata in Tavola. 3.6.

Tabella 3.6

|

X |

X |

||||||

|

si 3 |

si 2 |

si 1 |

si 3 |

si 2 |

si 1 |

||

Il funzionamento dell'encoder è descritto da tre funzioni A 3, e 2,y 1, ciascuno dei quali è uguale a uno su quattro set (il numero del set corrisponde al numero di input). I sovDNF delle funzioni di uscita sono:

Tre funzioni sono implementate da tre disgiuntori (Fig. 3.15), alle cui uscite si forma un codice binario a tre cifre.

Riso. 3.15.

Allo stesso tempo, l'argomento X 0 non è incluso in nessuna delle funzioni logiche e del bus X 0 rimane inutilizzato. Infatti, il segnale di ingresso x0 deve corrispondere al codice "000", che sarà ancora in uscita dall'encoder se tutti gli altri argomenti sono zero.

Oltre agli encoder convenzionali, ci sono anche codificatori di priorità. Tali codificatori eseguono un'operazione più complessa. Durante il funzionamento di computer e altri dispositivi, viene spesso risolto il problema di determinare un concorrente prioritario per il servizio. Diversi concorrenti inviano contemporaneamente le loro richieste di servizio che non possono essere soddisfatte. Devi scegliere chi riceve il servizio prioritario. La versione più semplice del problema consiste nell'assegnare una priorità fissa a ciascuna fonte di richieste. Ad esempio, un gruppo di otto richieste R 7, ..., R 0 (R - dall'inglese. richiesta – richiesta) è formato in modo che la fonte numero sette abbia la priorità più alta, e poi la priorità diminuisce da numero a numero. L'origine del proiettile ha la priorità più bassa: verrà servita solo se tutte le altre richieste sono assenti. Se ci sono più richieste contemporaneamente, viene servita la richiesta con il numero maggiore.

Il codificatore di priorità emette il numero binario della richiesta più alta. Con un solo ingresso eccitato, l'encoder prioritario funziona allo stesso modo di quello binario. Pertanto, nella serie IC, un codificatore binario come elemento indipendente può essere assente. La sua modalità di funzionamento è un caso speciale dell'encoder prioritario.

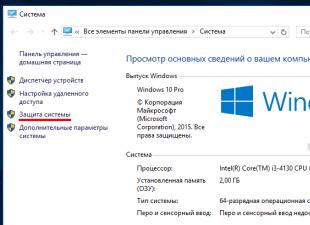

sushiandbox.ru Mastering PC - Internet. Skype. Mezzi sociali. Lezioni su Windows.

sushiandbox.ru Mastering PC - Internet. Skype. Mezzi sociali. Lezioni su Windows.