Procesorové jadro mikrokontrolérov:

– aritmeticko-logická jednotka

- organizácia pamäti

Dobrý deň milí rádioamatéri!

Vítam vás na stránke ""

Dnes (presnejšie v priebehu niekoľkých článkov) sa na to pozrieme bližšie základ akýkoľvek mikrokontrolér – jadro procesora.

Podstatné prvky:

1. Aritmetická logická jednotka

ALU- srdce (a možno aj myseľ, so cťou a svedomím) mikrokontroléra.

Nebudeme tu vstupovať do role „maniakálneho rozkúskovania“ a hrabania sa vo vnútri tohto zariadenia. Dozvedáme sa len, že vďaka ALU prebieha všetka práca mikrokontroléra. Ak budete mať niekedy túžbu dozvedieť sa hlbšie, ako funguje „srdce“ mikrokontroléra (a bude pekné, ak sa objaví), potom v knihách úžasných autorov Belova, Ryumika, Evstifeeva, Revicha, Baranova a mnohých ďalších , vždy nájdete podrobnú odpoveď .

2. Pamäť mikrokontroléra (organizácia pamäte)

Predtým, ako zvážime pamäť mikrokontroléra, povedzme si niečo o pamäti všeobecne.

Ľudská pamäť - s ňou je všetko jasné - môže byť „pevná“ (keď ste v pevnej pamäti a niekedy dokonca aj v správnej mysli) a, bohužiaľ, „deravá“. A všetky informácie sú uložené v takzvaných „neurónoch“ – malých pamäťových bunkách.

S mikrokontrolérmi je takmer všetko rovnaké. Iba ak má osoba najmenšiu bunku na ukladanie informácií nazývanú „neurón“. najmenšia pamäťová bunka pre mikrokontrolér ukladanie informácií sa nazýva " trocha“.

Jeden bit môže uložiť buď jednu logickú jednotku alebo jednu logickú nulu.

Trocha

– minimálna merná jednotka pre množstvo pamäte v mikroprocesorovej technológii.

Ďalšou hlavnou alebo najbežnejšou jednotkou pamäte je byte.

Byte – to je osem bitov informácií. Do jedného bajtu je možné uložiť iba osem núl a jednotiek.

Maximálny počet, ktorý je možné zapísať do bajtu, je 255. Ak v programe operujete veľké čísla potom by ste mali vedieť (aby ste vedeli, koľko bajtov je potrebných na uloženie čísla), že maximálne číslo, do ktorého je možné zapísať:

– jeden bajt = 255

– dva bajty = 65535

– tri bajty = 16 777 215

- štyri bajty - číslo viac ako 4 miliardy (ak nie ste aspoň sto z časopisu Forbes, potom nebudete potrebovať štyri bajty pamäte na ukladanie čísel).

Zápis do pamäte a čítanie z pamäte prebieha v bajtoch (nemôžete zapísať ani prečítať jeden bit informácie).

Ďalšou mernou jednotkou je kilobajt.

V kilobajte je 1024 bajtov informácií.

(presne 1024, nie 1000 bajtov).

Existujú aj veľké hodnoty na meranie množstva pamäte (megabajty, gigabajty), ale zatiaľ sa nepoužívajú v mikrokontroléroch.

Dúfam, že s jednotkami merania elektronickej pamäte je nám všetko jasné:

Organizácia pamäte v mikrokontroléri

Čipy AVR majú tri typy pamäte:

– programová pamäť alias FLASH pamäť

– dátová pamäť, známa ako RAM

(RAM)aka SRAM

– energeticky nezávislá pamäť, aka EEPROM, aka EEPROM

Mikrokontrolér má tri adresné priestory v ktorých sa nachádzajú vyššie uvedené typy pamätí. Zároveň sa ukázalo, že dátová pamäť (v zmysle prideleného adresného priestoru) je trochu ochudobnená - musí zdieľať svoj adresný priestor s pamäťovými bunkami, v ktorých sú uložené registre. všeobecný účel a I/O registre (podrobne sa o nich dozviete v ďalšom článku). Tieto registre fyzicky nepatria do dátovej pamäte, ale sú v rovnakom adresnom priestore. Ak štartovacie adresy programovej pamäte a energeticky nezávislej pamäte začínajú na adrese nula, potom štartovacia adresa dátovej pamäte nezačína na adrese nula - univerzálne registre a I/O registre zaujmú svoje miesta od adresy nula a iba oni za nimi nasledujú adresy pamäťových buniek programu.

Niektoré typy ATiny MCU nemajú dátovú pamäť.

Programová pamäť (FLASH pamäť)

Pamäť programu je navrhnutý tak, aby v ňom boli uložené naše programy, ako aj všetky potrebné údaje, ktoré sa počas vykonávania programu nemenia (konštanty). Po vypnutí napájania mikrokontroléra sa všetky údaje v pamäti programu uložia.

Pamäť programu, samozrejme, majú všetky mikrokontroléry. Veľkosť programovej pamäte sa v závislosti od typu MK pohybuje od 1 kilobajtu do 256 kilobajtov.

Prístup do pamäte programu má pri programovaní MK len programátor, do programovej pamäte má prístup aj samotný MK, ale len na čítanie údajov z pamäte, nemôže tam nič zapisovať (nikdy nevieš, zrazu nám chce pokaziť program). Je pravda, že MK rodiny Mega má možnosť (s povolením programátora) vykonať zmeny v pamäti programu, ale toto je iný príbeh.

Pre programovú pamäť existujú ďalšie dva typy merania pamäte - “ slovo"A" stránku“.

Faktom je, že programová pamäť pozostáva z buniek pozostávajúcich z dvoch bajtov. Takáto bunka sa nazýva „slovo“. A to sa robí týmto spôsobom, pretože takmer všetky príkazy MK pozostávajú z dvoch bajtov, a preto sú na ich zápis potrebné dva bajty v pamäti programu. Každý príkaz MK je jedno „slovo“. Existuje niekoľko príkazov, ktoré vyžadujú na zápis 4 bajty pamäte - dve slová, ale takéto príkazy sa nachádzajú v MK s pamäťou programu väčšou ako 8 kilobajtov.

teda do jednej bunky programovej pamäte možno zapisovať:

- akýkoľvek príkaz pozostávajúci z dvoch bajtov

- polovica príkazu pozostávajúca zo 4 bajtov

- dve konštanty, z ktorých každá sa zmestí do jedného bajtu alebo do jednej šestnásťbitovej konštanty. Zároveň, ak do pamäte zapíšete tri jednobajtové konštanty, budú v pamäti stále zaberať štyri bajty (dve slová).

okrem toho zápis do programovej pamäte sa vykonáva nielen „slovami“, ale aj „stránkami“

. Veľkosť stránky je od 64 do 256 bajtov (čím väčšia je veľkosť programovej pamäte, tým väčšia je „stránka“). Čo to znamená. Ak vytvoríte malý program, ktorý má 11 slov (22 bajtov), stále zaberie jednu stránku programovej pamäte, t.j. aspoň 64 bajtov. „Extra“ 42 bajtov bude vyplnených nulami alebo jednotkami. Toto sú koláče.

To však nie je všetko.

Pamäť programu môže mať tri stavy(ak to tak môžem povedať):

1. Celá pamäť je k dispozícii programátorovi

V tomto prípade môžeme celú pamäť úplne zaplniť naším programom a dátami. A program sa spustí od nulovej adresy pamäte.

2. Časť pamäte zaberá MK

V prípade, že sa počas prevádzky používa MK (a dúfam, že si pamätáte čo to je), MK si pre potreby spracovania prerušenia vezme časť pamäte a uloží ju do nej “ vektory prerušenia“.

Čo to je.

Keď MK umožníme spracovávať prerušenia, počnúc od nulovej adresy pamäte vezme niektoré bunky, aby do nich uložil adresy, do ktorých musí MK prejsť, aby vykonal rutinu prerušenia. Pre každé prerušenie MK pridelí dva bajty pamäte (jedno slovo), v ktorých sú uložené adresy rutín prerušenia. Tieto adresy, ktoré označujú, kde sa v pamäti nachádza podprogram na spracovanie toho alebo toho prerušenia, sa nazývajú „ vektory prerušenia“. A celá oblasť pamäte, v ktorej sú uložené „vektory prerušenia“, sa nazýva vektorová tabuľka prerušenia. Počet obsadených pamäťových buniek pre prerušenia priamo závisí od počtu možných prerušení pre daný mikrokontrolér (od niekoľkých po niekoľko desiatok). Všetky prerušenia sú umiestnené na začiatku programovej pamäte, od adresy nula, a majú jasnú postupnosť. Na adrese nula sa vždy nachádza vektor prerušenia resetovania. Keď zariadenie zapneme, alebo resetujeme tlačidlom, spustí sa prerušenie resetu. MK načíta z nulovej adresy (z bunky) adresu, ktorá udáva, kde v pamäti sa nachádza začiatok nášho programu a prechodom na túto adresu začne program vykonávať. Samotný program sa v tomto prípade bude nachádzať v pamäti programu hneď za tabuľkou prerušení.

3. MK zoberie ďalšiu časť pamäte programu (presnejšie nezoberie, ale na konci pamäte pridelí oblasť, do ktorej programátor umiestni špeciálny program - „loader“).

To je možné v MCU rodiny „MEGA“, ktoré majú schopnosť umožniť MCU vykonávať zmeny v pamäti programu.Čo to znamená.

Niektorí MK majú schopnosť samoprogram. V praxi amatérov sa táto možnosť MK využíva extrémne zriedkavo. Schopnosť preprogramovania (samoprogramovania) je potrebná hlavne v prípadoch priemyselnej výroby zariadenia na mikrokontroléri, pre ktorý môže byť následne uvoľnená aktualizácia softvér. O tejto možnosti nebudeme uvažovať, aspoň zatiaľ. Potrebujeme len vedieť, že v MK, ktoré podporujú samoprogramovanie, je pamäť programu rozdelená na dve časti

:

- horná - sekcia aplikačného programu, kde sa nachádza náš program a prerušovať vektory

- nižšie - sekcia bootloader (Boot Loader Section- v angličtine), kam programátor umiestni svoj načítavací program. Veľkosť sekcie zavádzača závisí od celkovej veľkosti pamäte programu MK a môže sa pohybovať od 128 bajtov do 4096 bajtov. Ak nevyužijeme možnosť samoprogramovania MK, tak táto časť je uvedená pre náš program a dáta.

Pamäť FLASH sa nazýva programová, pretože je vyrobená pomocou takzvanej technológie Flash (ako bežné počítačové „flash disky“ pre nás všetkých).

Pamäť programu umožňuje 10 000 cyklov preprogramovania.

Dátová pamäť (statická RAM, SRAM)

RAM, to je dátová pamäť typu SRAM, určený na ukladanie rôznych údajov získaných v dôsledku programu.

Po vypnutí napájania mikrokontroléra sa stratia všetky údaje v ňom uložené.

Dátová pamäť je k dispozícii takmer vo všetkých mikrokontroléroch (v najjednoduchších MK z rodiny Tiny chýba).

Vo všetkých MC z rodiny Mega (a v časti MC z rodiny Tiny) sa množstvo vstavanej dátovej pamäte pohybuje od 128 bajtov do 8 kilobajtov a takmer všetku máme k dispozícii. Na usporiadanie stohu je potrebné len trochu MK (čo to je, zistíme neskôr). Niektoré MK poskytujú pripojenie externá pamäť(môže byť akéhokoľvek typu - FLASH, SRAM, EEPROM) až do 64 kilobajtov. V prípade pripojenia externej pamäte v takýchto MK sa stáva akoby pokračovaním dátovej pamäte.

Zápis do dátovej pamäte a čítanie z nej prebieha bajt po byte a na rozdiel od programovej pamäte nie je rozdelená na stránky a slová.

Energeticky nezávislá pamäť (EEPROM)

Energeticky nezávislá pamäť tiež odkazuje na dátovú pamäť, ale na rozdiel od druhej má niekoľko funkcií. Je určený na ukladanie údajov a konštánt, ktoré sa musia zachovať pri výpadku napájania.

Všetky mikrokontroléry majú EEPROM.

Keď sa vypne napájanie mikrokontroléra, všetky dáta uložené v energeticky nezávislej pamäti sa uložia (preto sa nazýva energeticky nezávislá).

Množstvo energeticky nezávislej pamäte, v závislosti od typu MK, sa pohybuje od 64 bajtov do 4 kilobajtov.

Písanie a čítanie informácií do pamäte sa vykonáva bajt po bajte. Avšak v starších modeloch rodiny MEGA má energeticky nezávislá pamäť, ako aj programová pamäť, záznam stránky. Veľkosť stránky je malá, iba 4 bajty. V praxi na tejto funkcii nezáleží - zápis aj čítanie sa stále vykonáva bajt po bajte.

Počet cyklov zápisu a vymazania pamäť dosahuje 100 000.

Hlavnou črtou EEPROM je, že keď sa do nej zapisujú dáta, stáva sa veľmi „pomalým“ – zápis jedného bajtu môže trvať od 2 do 4 milisekúnd (to je veľmi nízka rýchlosť) a môže sa stať, že napr. - alebo prerušenie, v takom prípade sa proces zápisu údajov zničí.

Navyše sa neodporúča zapisovať dáta do energeticky nezávislej pamäte od adresy nula (nepamätám si zdroj tejto informácie, ale presne si pamätám, čo som niekde čítal) - dáta sa môžu počas prevádzky MK poškodiť. . Niekedy programátori ustúpia niekoľko bajtov od začiatku pamäte a až v ďalších bunkách začnú zapisovať údaje.

Srdcom každej flash-pamäte je kremíkový kryštál, na ktorom sú vytvorené nie celkom bežné tranzistory s efektom poľa. Takýto tranzistor má dve izolované hradla: riadiace (riadiace) a plávajúce (plávajúce). Ten je schopný držať elektróny, to znamená nabíjať. V článku, ako v každom tranzistore s efektom poľa, je kolektor a zdroj (obr. 4.1). V procese zápisu sa na riadiacu bránu privádza kladné napätie a časť elektrónov pohybujúcich sa z odtoku do zdroja sa odkláňa do plávajúcej brány. Časť elektrónov prekoná vrstvu izolátora a prenikne (difunduje) do plávajúcej brány. Môžu tam zostať dlhé roky.

Koncentrácia elektrónov v oblasti plávajúcej brány určuje jeden z dvoch stabilných stavov tranzistora - pamäťovú bunku. V prvom, počiatočnom stave, je počet elektrónov na plávajúcom hradle malý a prahové napätie na otvorenie tranzistora je relatívne nízke (logická jednička). Keď je na plávajúcu bránu naložený dostatok elektrónov, tranzistor je v druhom ustálenom stave. Jeho otváracie napätie sa prudko zvyšuje, čo zodpovedá logickej nule. Pri čítaní sa meria

Ryža. 4.1. Flash pamäťová bunka

prahové napätie, ktoré musí byť privedené na odtok, aby sa zapol tranzistor. Na odstránenie informácií sa na kontrolnú bránu krátko privedie záporné napätie a elektróny z plávajúcej brány sa rozptyľujú späť do zdroja. Tranzistor opäť prejde do stavu logickej jednotky a zostane v ňom až do vykonania ďalšieho zápisu. Je pozoruhodné, že vo flash pamäti jeden tranzistor ukladá jeden bit informácie - je to bunka. Celý proces „zapamätania“ je založený na difúzii elektrónov v polovodiči. To vedie k dvom nie príliš optimistickým záverom.

Doba skladovania nabitia je veľmi dlhá a meria sa v rokoch, ale stále je obmedzená. Zákony termodynamiky a difúzie hovoria, že koncentrácia elektrónov v rôznych oblastiach sa nakoniec vyrovná.

Z rovnakého dôvodu je počet cyklov zápisu a prepisu obmedzený: od stotisíc po niekoľko miliónov. Časom nevyhnutne nastáva degradácia samotného materiálu a p-n-prechody. Napríklad karty Kingston Compact Flash sú dimenzované na 300 000 cyklov zápisu. Kompaktný blesk Transcend – zapnutý

1 000 000, zatiaľ čo USB flash disk Transcend 32 Gb je len 100 000.

Existujú dve architektúry flash pamäte. Líšia sa v spôsobe prístupu k bunkám a podľa toho aj v organizácii vnútorných vodičov.

Pamäť NOR (ALEBO-NIE) vám umožňuje pristupovať k bunkám po jednej. Každá bunka má samostatný vodič. Adresový priestor pamäte NOR vám umožňuje pracovať s jednotlivými bajtmi alebo slovami (každé slovo obsahuje

2 bajty). Táto architektúra ukladá vážne obmedzenia maximálneho množstva pamäte na jednotku plochy čipu. Pamäť NOR sa v súčasnosti používa iba v čipoch BIOS a iných nízkokapacitných ROM, ako sú mobilné telefóny.

V pamäti NAND (NAND) je každá bunka v priesečníku „bitovej čiary“ a „riadky slova“. Bunky sú zoskupené do malých blokov podobných zhluku pevný disk. Čítanie aj písanie sa vykonáva iba v celých blokoch alebo riadkoch. Všetko moderné vymeniteľné médiá postavené na pamäti NAND.

Najväčšími výrobcami NAND čipov sú Intel, Micron Technology, Sony a Samsung. Rozsah vyrábaných čipov je pomerne veľký a niekoľkokrát do roka sa aktualizuje.

Ovládače

Pamäťový radič slúži na riadenie čítania a zápisu. V súčasnosti je ovládač vždy implementovaný ako samostatný prvok (je to buď mikročip niektorého zo štandardných tvarových faktorov, alebo nerozbalený čip vložený do pamäťovej karty), aj keď sa pracuje na integrácii ovládača priamo do flash pamäťového čipu. .

Ovládače sú navrhnuté a vyrobené pre úplne špecifické flash pamäťové čipy. Spôsob adresovania buniek je konštrukčne zabudovaný v ovládači. Pri zápise na flash pamäťový čip sú dáta usporiadané určitým spôsobom, ktorý sa líši model od modelu. Výrobcovia udržiavajú tieto jemnosti v tajnosti a zjavne ich neplánujú zverejniť. Je zrejmé, že sa vytvára oveľa viac firmvéru ovládačov ako samotných modelov ovládačov. Firmvér ovládača (firmvér) a tabuľka prekladu adries (prekladač) sa zapisujú do servisnej oblasti pamäte flash. Je to oblasť, ktorú ovládač začne čítať ihneď po pripojení napájania. Okrem samotného adresovania článkov plní regulátor množstvo ďalších funkcií: funkcie sledovania chybných sektorov, korekcie chýb (ECC - error check and correct) a rovnomerného opotrebovania článkov (wear leveling).

Technologickou normou pri výrobe pamäťových čipov je prítomnosť v priemere až 2 % nepracujúcich buniek v nich. Postupom času sa ich počet môže zvýšiť, preto, rovnako ako v prípade pevných diskov, je v pamäti flash k dispozícii rezervný objem. Ak sa objaví chybný sektor, radič počas formátovania alebo zápisu nahradí svoju adresu v tabuľke prideľovania súborov adresou sektora z náhradnej oblasti. Korekciu vykonáva kontrolér, ale realizuje sa na úrovni súborového systému konkrétneho média.

Kvôli obmedzenému zdroju článkov (rádovo niekoľko miliónov cyklov čítania/zápisu pre každý) má ovládač funkciu, ktorá zohľadňuje rovnomernosť opotrebovania. Aby sa zabezpečilo rovnomerné zaznamenávanie informácií, voľný priestor je podmienečne rozdelený na sekcie a pre každú z nich sa berie do úvahy počet operácií zápisu. Štatistika cyklu sa zaznamenáva v skrytej obslužnej oblasti pamäte a ovládač pravidelne pristupuje k týmto informáciám. Nemá to vplyv na adresovanie.

Štruktúra USB flash disku

Napriek rôznorodosti prípadov sú všetky USB flash disky navrhnuté rovnakým spôsobom. Ak sú polovice puzdra spojené západkou, zvyčajne sa ľahko rozdelia. Vodotesné alebo trendy puzdrá sa musia otvárať deštruktívnymi metódami, ako je rezanie.

Na doske vo vnútri USB flash disku (obr. 4.2) sú nevyhnutne dva mikroobvody: pamäťový čip a ovládač. Obe sú továrensky označené. Niekedy doska nesie dva flash pamäťové čipy, ktoré pracujú v pároch. Potrubie mikroobvodov pozostáva z niekoľkých rezistorov a diód, výkonového stabilizátora a kremenného rezonátora. Stabilizátor sa v poslednej dobe čoraz viac integruje priamo do ovládača a počet nástavcov sa znižuje na minimum. Okrem toho môže doska obsahovať led indikátor a mini prepínač na ochranu proti zápisu.

Ryža. 4.2. Zariadenie flash disku

USB konektor je prispájkovaný priamo na doske. Spájkovacie body kontaktov v mnohých modeloch sú dosť zraniteľné, pretože znášajú mechanické zaťaženie pri pripájaní a odpájaní zariadenia.

Typy a prevedenie pamäťových kariet

Mnoho spoločností z času na čas ponúka používateľom rôzne dizajny pamäťových kariet. Až na zriedkavé výnimky sú všetky navzájom nekompatibilné z hľadiska počtu a usporiadania kontaktov a elektrické charakteristiky, Karty Flash sa dodávajú v dvoch typoch: s paralelným (paralelným) a sériovým (sériovým) rozhraním.

V tabuľke. Tabuľka 4.1 uvádza 12 hlavných typov pamäťových kariet, ktoré sa v súčasnosti nachádzajú. V rámci každého typu existujú ďalšie odrody, berúc do úvahy, že môžeme hovoriť o existencii takmer 40 typov kariet.

Tabuľka 4.1. Typy pamäťových kariet

|

Typ pamäťovej karty |

Celkové rozmery, mm) |

Maximálne konštruktívny |

Rozhranie |

|

Kompaktný blesk (CF) |

Paralelné 50 kolíkov |

||

|

Sériové 9 piny |

|||

|

Multimediálna karta (MMS) |

Sériové 7 piny |

||

|

Sériové 7 piny |

|||

|

Vysokorýchlostné mms |

Sériové 13 piny |

||

|

Sériové 10 piny |

|||

|

Memory Stick PRO |

Sériové 10 piny |

||

|

Memory Stick Duo |

Sériové 10 piny |

||

|

SmartMedia (SSFDC) |

Paralelné 22 kolíkov |

||

|

Paralelné 22 kolíkov |

|||

|

Sériové 8 piny |

Karty MMC môžu pracovať v dvoch režimoch: MMC (MultiMedia Card) a SPI (Serial Peripheral Interface). Režim SPI je súčasťou protokolu MMC a používa sa na komunikáciu s kanálom SPI v mikrokontroléroch od spoločnosti Motorola a niektorých ďalších výrobcov.

Do slotu pre kartu SD (Secure Digital) môžete vložiť MMS karta(MultiMedia Card), ale nie naopak. Ovládač SD kariet obsahuje hardvérové šifrovanie dát a samotná pamäť je vybavená špeciálnou oblasťou, v ktorej je uložený šifrovací kľúč. Stalo sa tak s cieľom zabrániť nelegálnemu kopírovaniu hudobných nahrávok, na uchovávanie a predaj takýchto nosičov bol koncipovaný. Karta má ochranný spínač proti zápisu.

Karty CompactFlash (CF) možno jednoducho vložiť do slotu PCMCIA Type II. Hoci PCMCIA má 68 pinov a CF len 50, dizajn CompactFlash karty poskytuje plnú kompatibilitu a má všetky funkcie formátu PCMCIA-AT A.

Všetky médiá Memory Stick (štandard Sony) sú relatívne kompatibilné. Štandard teoreticky počíta s kapacitou pamäťovej karty až 2 TB, aj keď v skutočnosti kapacita dosahuje jednotky gigabajtov.

Karty SmartMedia sú prakticky zastarané, nachádzajú sa len vo veľmi starých digitálnych fotoaparátoch. Je pozoruhodné, že to bol jediný štandard, v ktorom sa ovládač nenachádzal vo vnútri karty, ale v čítačke.

Konštrukcia pamäťových kariet je neoddeliteľná - ide o zariadenie nevhodné na opravu. Nebalené mikroobvody spolu so závermi sa nalejú do hmoty a všetky sa vtlačia do plastového obalu. Jediný spôsob, ako sa dostať ku kryštálu, je otvorenie zariadenia, ale poškodenie vodičov je takmer nevyhnutné.

Čitatelia

Ak chcete čítať USB flash disk, normálne USB vstup: počítač považuje takéto zariadenia za štandardné vymeniteľný disk vďaka ich ovládaču. Ovládače všetkých pamäťových kariet sú k počítaču adresované sériovým alebo paralelným rozhraním - kontaktmi na karte. Pre každé z týchto rozhraní je potrebný zodpovedajúci adaptér - prídavný ovládač, ktoré zodpovedá tomuto rozhraniu so štandardným portom USB.

Čítačka kariet je zariadenie pozostávajúce z jedného alebo viacerých podobných ovládačov, napájacieho meniča a konektorov pre rôzne pamäťové karty (obr. 4.3). Napájanie je dodávané zo zdroja +5 V cez USB kábel.

Ryža. 4.3. čítačka pamäťových kariet

Najčastejšie existujú "kombináty" určené pre niekoľko typov kariet: od 6 do 40. V čítačke kariet je oveľa menej slotov, pretože každý slot sa používa pre niekoľko typov kariet, ktoré sú podobné veľkosťou a umiestnením kontaktov. Podľa jeho vlastností rôzne modely sú prakticky ekvivalentné, líšia sa však najmä počtom podporovaných typov kariet a dizajnom.

Logická organizácia

Predtým, ako prejdeme k súborovým systémom flash diskov, musíme si spomenúť na architektúru NAND. V tejto často používanej pamäti prebieha čítanie, zápis a mazanie informácií iba v blokoch.

Na pevných a disketových diskoch je veľkosť bloku 512 bajtov, nepočítajúc 59 servisných bajtov, ktoré sú viditeľné iba pre radič pevného disku. Všetky súborové systémy boli vytvorené s ohľadom na tieto hodnoty. Problém je v tom, že vo flash pamäti veľkosť vymazávacieho bloku až na zriedkavé výnimky nezodpovedá veľkosti štandardného sektora disku 512 bajtov a zvyčajne je 4,8 alebo dokonca 64 KB. Na druhej strane, kvôli kompatibilite musí blok čítania/zápisu zodpovedať veľkosti sektora disku.

Na tento účel je blok vymazania rozdelený na niekoľko blokov na čítanie / zápis s veľkosťou 512 bajtov. V praxi je blok o niečo väčší: okrem 512 bajtov pre dáta má aj „chvost“ (Tail) dlhý 16 bajtov pre servisné informácie o samotnom bloku. Fyzicky nie je umiestnenie a počet blokov čítania/zápisu ničím obmedzené. Jediným obmedzením je, že blok na čítanie/zápis nesmie prekročiť hranicu bloku vymazania, pretože nemôže patriť do dvoch rôznych blokov na vymazanie.

Bloky čítania/zápisu sú rozdelené do troch typov: platné, neplatné a chybné. Bloky, ktoré obsahujú zaznamenané údaje a patria do súboru, sú platné. Použité bloky so zastaranými informáciami sa považujú za neplatné a musia byť vymazané. Kategóriu chybných blokov tvoria bloky, ktoré sa nedajú zapísať a vymazať.

Ďalšou vlastnosťou flash pamäte je, že informácie možno zapisovať iba do priestoru, ktorý bol predtým vyčistený od predchádzajúcich informácií. Keď je potrebné zapísať informácie, firmvér ovládača sa musí rozhodnúť, ktoré neplatné bloky sa majú vymazať ako prvé. Vo väčšine mikroprogramov je otázka odstraňovania neplatných blokov riešená najjednoduchším spôsobom: akonáhle sa určitá časť kapacity flash disku naplní informáciami, automaticky sa spustí mechanizmus na čistenie neplatných blokov.

Na zvýšenie životnosti pamäte sa používa technológia kontroly vyrovnávania opotrebovania, ktorá predlžuje životný cyklus pamäťový kryštál vďaka rovnomernému rozdeleniu cyklov zápisu / vymazania pamäťových blokov. Vedľajší efekt – zlyhanie jedného pamäťového bloku – neovplyvňuje činnosť ostatných pamäťových blokov toho istého kryštálu. Pevné bloky patria k súborom, ktoré neboli dlho alebo vôbec zmenené alebo presunuté. Prítomnosť pevných dátových blokov vedie k tomu, že zostávajúca časť buniek je vystavená zvýšenému opotrebovaniu a rýchlejšie spotrebúva svoje zdroje. Firmvér berie do úvahy takéto bloky a podľa potreby presúva ich obsah do iných buniek.

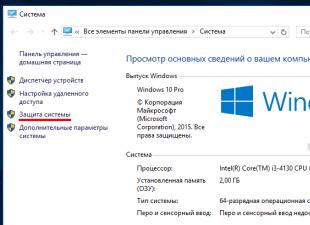

Súborové systémy flash diskov a pamäťových kariet sú na prvý pohľad používateľom dobre známe z pevných diskov a diskiet. Toto je FAT16, menej často FAT32: takto operačný systém Windows navrhuje formátovanie disku. Štandardné prostriedky Disk Windows XP a Windows 7 je možné naformátovať systém NTFS! Ak to chcete urobiť, musíte najskôr prejsť do Správcu zariadení a v okne vlastností pripojeného flash disku na karte Politika vybrať hodnotu Optimalizácia pre rýchle spustenie. Špeciálne programy od výrobcov, ako napríklad HP USB Disk Storage Format Tool, umožňujú formátovať flash disky na NTFS bez vynaloženia takéhoto úsilia.

Avšak vonkajšia podobnosť súborových systémov disky SSD a konvenčné pevné disky klamú. Súborový systém flash pamäte (Flash File System, FFS) iba emuluje konvenčnú diskovú jednotku a pozostáva z riadiacich jednotiek a inicializačnej jednotky. V skutočnosti iba ovládač flash disku alebo pamäťovej karty vie o skutočnom umiestnení a adresovaní pamäťových blokov.

To je veľmi dôležité, keď rôzne cesty obnovenie obsahu pamäťového flash čipu. Pri čítaní pamäťového čipu prostredníctvom jeho "natívneho" radiča obsahuje obrazový súbor sekvenciu blokov v poradí podľa ich čísel alebo posunov. Na začiatku je hlavička a tabuľka súborového systému. Ak sa čítanie vykonáva na programátore, počiatočné bloky výpisu obsahujú servisné informácie a dátové bloky sú zmiešané takmer náhodne. Zároveň je nepravdepodobné, že by servisné informácie boli užitočné, pretože úplne závisia od modelu ovládača a jeho firmvéru - správna postupnosť blokov sa musí zostaviť s veľkými ťažkosťami.

Niektoré fotoaparáty pracujú iba so súborom RAW systém Spôsob nahrávania fotografií na médiá s takýmto systémom súborov, ako aj funkcie formátovania samotnej karty závisia od modelu zariadenia a dokonca aj od firmvéru konkrétneho modelu. Tento formát nie je štandardizovaný a má veľa variácií. Dáta z takýchto kariet dokážu obnoviť väčšinou len servisné programy od výrobcu fotoaparátu a ako čítačku kariet je vhodné použiť samotný fotoaparát.

Ryža. 4.4. Formátovať okno flash disku Windows Vista SPl

Inovácia je systém súborov exFAT (Extended FAT - rozšírený FAT). Podpora pre tento súborový systém, špeciálne navrhnutý pre flash disky, sa prvýkrát objavila vo Windows Embedded CE 6.0. Windows Vista Service Pack 1 a Windows 7 fungujú s exFAT (obrázok 4.4).

Účelom nového súborového systému je postupná výmena FAT a FAT32 na flash diskoch. Obsahuje niektoré funkcie, ktoré boli predtým jedinečné pre súborový systém NTFS:

Limit veľkosti súboru 4 GB bol prekonaný: teoretický limit je 2^ bajtov (16 exabajtov);

Vylepšená distribúcia voľné miesto zavedením bitovej mapy voľného miesta, ktorá znižuje fragmentáciu disku;

Obmedzenie počtu súborov v jednom adresári bolo odstránené;

Pridaná podpora pre zoznam prístupových práv.

Ako skoro sa tento súborový systém stane normou pre flash disky, ukáže čas. Podľa všetkého sa tak nestane skôr operačný systém Windows 7 prevezme drvivá väčšina používateľov.

Niekedy pri vývoji zariadenia je potrebné uložiť niektoré údaje do energeticky nezávislej pamäte. V takýchto prípadoch sa zvyčajne používa interná EEPROM mikrokontroléra. Ak to nestačí, tak sa väčšinou používajú externé čipy EEPROM zo série 24lxx. Mikroobvody tejto série sú veľmi obľúbené. Najčastejšie ich možno nájsť v starom veku mobilné telefóny, niektoré základné dosky, kazety z tlačiarní a mnoho ďalších miest. Cena týchto čipov je tiež veľmi atraktívna. Napríklad 24LC16 stojí 11 rubľov.

Tento mikroobvod je dostupný v rôznych baleniach, z ktorých najobľúbenejšie sú DIP a SOIC. Mikroobvod má nasledujúci vývod:

Ako vidíte, existuje len veľmi málo záverov. Skúsme teda prísť na to, čo je čo.

A0, A1, A2- sa v tomto mikroobvode nepoužívajú. Môžu byť pripojené na zem alebo na napájanie plus. V niektorých iných mikroobvodoch série 24lxx môžu tieto kolíky nastaviť adresu mikroobvodu, aby bolo možné pripojiť až 8 pamäťových mikrónov na jednu i2c zbernicu naraz.

Vss- Zem.

SDA- dátová linka

SCL- hodinová pulzná linka

WP- Ochrana proti zápisu. Keď je tento pin logická 0, zápis do pamäte je povolený. Ak použijete logickú jednotku, potom je možné iba čítanie z pamäte.

Vcc- napájanie mikroobvodu. Podľa údajového listu je napájaný napätím od 2,5 voltu do 5,5 voltu.

Pripojenie k ovládaču.

Pripojenie pamäte k MK je veľmi jednoduché. Z páskovania je potrebná iba dvojica rezistorov s odporom asi 4,7 kOhm.

softvér

Na prácu s pamäťou bola vyvinutá knižnica, ktorá implementuje nasledujúce funkcie:

i2c_init- upravuje rýchlosť hodinových impulzov idúcich pozdĺž linky SCL.

Čip 24LC16 podporuje frekvencie až do 400 kHz. Frekvenciu môžete vypočítať takto:

![]()

Frekvencia hodín CPU- frekvencia, na ktorej mikrokontrolér pracuje

TWBR- číslo zapísané v rovnomennom registri.

TWPS- predurčovač. Hodnoty preddeličky sa nastavujú bitmi TWPS1 a TWPS0 v registri TWSR.

Pre ovládač Atmega 32 platí nasledujúca tabuľka:

i2c_start- odošle úvodnú správu

i2c_stop- odošle správu o zastavení

i2c_send- odošle bajt

i2c_recive- prijíma bajt

i2c_recive_last- zaberie posledný bajt. Rozdiel oproti predchádzajúcej funkcii je v tom, že pri príjme bajtu mikrokontrolér nepošle potvrdzovací bit. Ak pri príjme posledného bajtu použite i2c_recive potom zostane vedenie SDA pritlačené k zemi.

Zápis údajov na pamäťový čip

Údaje môžete zapisovať v náhodnom poradí aj stránku po stránke. Keďže na zbernici i2c môže byť niekoľko zariadení naraz, pre prístup k akémukoľvek zariadeniu potrebujete poznať jeho sedembitovú adresu. Adresa čipu 24LC16 palcov binárna forma vyzerá takto:

Bity A,B,C sa používajú na výber pamäťového bloku. V čipe je 8 pamäťových blokov, každý má 256 bajtov. Preto bity ABC nadobúdajú hodnoty od 000 do 111.

Ak chcete zapísať bajty na čip, musíte vykonať nasledujúcu postupnosť akcií:

- Inicializujte rozhranie i2c

- Odoslať úvodnú správu

- Odoslať adresu čipu + adresu bloku pamäte

- Pošlite adresu miesta v pamäti, do ktorého sa má zapisovať

- Odoslať bajt údajov

- Pošlite stop balík

Príklad: Treba zapísať bajt 0xFA podľa adresy 0x101.

vyvolajte i2c_init

vyvolajte i2c_start

ldi teplota,0b 1010

001

0

// Adresa čipu, kde:

//

1010

- adresa čipu

//

001

- adresa pamäťového bloku (bunka 0x101 patrí do bloku 1)

//

0

zavolajte na i2c_send

ldi teplota 1 //Adresa pamäťovej bunky. (blok 1, bunka 1)

zavolajte na i2c_send

lditemp,0xFA //Načítajte bajt, ktorý sa má zapísať do registra

zavolajte na i2c_send //Zapíšte bajt

vyvolajte i2c_stop

Dáta do pamäte môžete zapisovať nielen bajt po byte, ale aj stránku po stránke. Veľkosť stránky je 16 bajtov. Zápis na stránku znamená nasledovné: Odoslanie adresy nulového bajtu požadovanú stránku a potom 16-krát odošleme potrebné údaje. Počítadlo adries sa automaticky zvýši o jednu. Ak odošlete dáta 17. krát, potom sa prepíše nulový bajt, ak pošlete bajt 18. krát, prepíše sa bajt číslo 1 atď.

Príklad: Je potrebné napísať prvú stranu bloku 0.

vyvolajte i2c_init //Inicializácia rozhrania i2c

vyvolajte i2c_start // Odoslať úvodnú správu

ldi teplota,0b 1010

000

0

// Adresa čipu, kde:

//

1010

- adresa čipu

//

000

- adresa pamäťového bloku (nás zaujíma nulový blok)

//

0

- bit čítania/zápisu. 0 - písať, 1 - čítať

zavolajte na i2c_send

ldi teplota, 16 //Adresa prvej stránky

zavolajte na i2c_send

ldi teplota, 0x01 //Načítanie bajtu číslo 0 do registra

zavolajte na i2c_send //Zapíšte bajt

ldi teplota,0x02 //Načítanie bajtu číslo 1 do registra

zavolajte na i2c_send //Zapíšte bajt

/// tu napíš zvyšok bajtov.....

ldi teplota,0x0E //Načítajte bajt číslo 14 do registra

zavolajte na i2c_send //Zapíšte bajt

ldi teplota,0x0F //Načítajte bajt číslo 15 do registra

zavolajte na i2c_send //Zapíšte bajt

vyvolajte i2c_stop //Odoslanie správy o zastavení

Čítanie údajov z čipu

Nejako sme prišli na záznam, teraz začneme čítať. Ak chcete prečítať bajt, postupujte takto:

- Inicializujte rozhranie i2c (ak ešte nebolo inicializované)

- Pošlite štartovací balíček

- Pošlite adresu mikroobvodu a adresu pamäťového bloku, odkiaľ budeme čítať

- Odoslať adresu umiestnenia pamäte

- Znova odošlite úvodnú správu

- Pošlite adresu čipu a adresu pamäťového bloku s bitom "read".

- Prijať bajt

- Pošlite stop balík

vyvolajte i2c_init //Inicializácia rozhrania i2c

vyvolajte i2c_start // Odoslať úvodnú správu

lditemp, 0b1010 011 0 // Adresa čipu + adresa 3. pamäťového bloku.

// Čítanie/zápis stále bit 0 !

zavolajte na i2c_send

ldi teplota, 0x41 //Adresa pamäťovej bunky

zavolajte na i2c_send

vyvolajte i2c_start //Opätovné odoslanie úvodnej správy

lditemp, 0b1010 011 1 // Adresa čipu + adresa pamäťového bloku + bit čítania / zápisu sa zmenil na 1

zavolajte na i2c_send // teraz môžete čítať údaje

zavolajte na i2c_recive_last //Prečítanie bajtu. Prvý a posledný.

vyvolajte i2c_stop //Odoslanie správy o zastavení

Čítanie je možné vykonávať postupne po byte, t.j. len zavolaji2c_recive Toľko, koľko potrebuje. Príkaz na zvýšenie adresy o jeden nie je potrebné odosielať. Prepínanie adries blokov počas sekvenčného čítania tiež nie je potrebné. Tie. môžete bez problémov zobrať a prečítať celý čip naraz.

Knižnica pre prácu s i2c bola vyvinutá a testovaná na mikrokontroléri Atmega32. Myslím, že to bude fungovať na mnohých iných ovládačoch bez akýchkoľvek zmien. Prirodzene, ovládač musí mať hardvérovú podporu pre i2c, alebo ako sa tiež nazýva TWI. Samozrejme, že i2c je možné implementovať aj programovo, ale neobťažoval som sa a nebolo to potrebné. Demo ukážkou je program, ktorý zapíše bajty od 0 do 15 do prvých 16 adries a po zapísaní ich vypíše na port A. Ako to funguje, môžete sledovať nielen naživo, ale aj v Proteuse.

A nakoniec prikladám oscilogram:

Takto vyzerá autobus i2c mojimi očami :-)

Všetky otázky a návrhy sú vítané v komentároch.

Ako príklad implementácie princípov priameho prístupu do pamäte (DMA) zvážte mikroobvod KR580VT57. Programovateľný ovládač PDP je určený na vysokorýchlostnú výmenu dát medzi systémovou pamäťou a štyrmi externými zariadeniami (ED).

Riadiaca jednotka vykonáva obojsmernú výmenu dát medzi pamäťou a JV (na žiadosť JV), pričom parametre určeného poľa adries pamäťových buniek (počiatočná adresa a počet cyklov) a riadiacich signálov sú generované v adresnom kanáli JV. mikroprocesorový systém. Každý zo štyroch kanálov radiča poskytuje adresovanie (inkrementáciou vygenerovanej adresy) externej pamäte s poliami s veľkosťou až 16K bajtov s možnosťou nastavenia ľubovoľnej zo 64K počiatočných adries.

Zloženie regulátora PDP

V regulátore možno rozlíšiť nasledujúce bloky (obr. 3.11.1): blok spracovania požiadaviek, generátor adries, logický blok čítania a zápisu, riadiaci blok, vyrovnávacia pamäť dát a dva registre - register nastavenia režimu a register stavu kanála. Zvážte ich vlastnosti.

Blok spracovania požiadaviek je určený pre:

● pre recepcia vyžiadacie signály ZDAP0–ZDAP3 na priamy prístup do pamäte z JV;

● pre maskovanie vstupy kanálov K0–K3;

● pre vydanie vyžiadanie potvrdzovacích signálov ¯PPDP0 – ¯PPDP3 priameho prístupu do pamäte, ktoré informuje JV o pripravenosti riadiacej jednotky na výmenu dát cez kanál DMA.

Generátor adries obsahuje 16-bitové registre počiatočnej adresy (PHA0…PHA3) a počtu cyklov (RCHTs0…RCHTs3), schému prírastku a znižovania a spúšťač. Počas vykonávania počiatočného inštalačného programu sa počiatočná adresa pamäťovej bunky, ku ktorej bude JV pristupovať cez kanál DMA, zapíše do RHA. Do 14 najmenej platných číslic registra počtu cyklov RFC sa zapíše číslo N - 1, kde N je počet cyklov. Dva najvýznamnejšie bity tohto registra sa používajú na riadenie výmeny cez kanál DMA.

V každom cykle sa z PHA načítajú dva bajty adresy. Spúšť poskytuje poradie čítania: horný bajt je odoslaný cez dátovú vyrovnávaciu pamäť do krokového motora a dolný bajt adresy je odoslaný cez zbernice A0 ... A3, A4 ... A7. Na konci cyklu schéma prírastok-zníženie zvýši obsah RHA a zníži obsah RFC o jeden. Je potrebné poznamenať, že výstupy regulátora A4…A7 sa vždy používajú ako výstupy pre bity A4…A7 kódu adresy a výstupy A0…A3 sa používajú:

- Ako výstupy na prenos najmenej významných číslic kódu adresy počas prevádzky DMA kanála;

- Ako vstupy na výber registra, s ktorým sa budú vymieňať informácie. Táto potreba vzniká pri zápise nastavovacieho programu do ovládača DMA, ako aj pri čítaní obsahu registra adries, registra počtu cyklov alebo stavového registra.

Logický blok čítania a zápisu

prijíma, generuje a vydáva signály, ktoré zabezpečujú výmenu informácií medzi procesorom a PDP radičom, pamäťou a JV. Logický blok čítania a zápisu má nasledujúce výstupy:

● ¯Зп - použitý trojsmerný riadiaci trojstabilný vstup/výstup:

Ako vchod pre príjem signálu z procesora záznamúdaje do interných registrov regulátora PDP pri jeho prvotnej inštalácii;

Ako VÝCHOD, na ktorom je generovaný signál, ktorý umožňuje externé zariadenie záznamúdaje z pamäte;

● ¯Th je obojsmerný trojstavový riadiaci vstup/výstup používaný:

Ako vchod prijímať signál z procesora, ktorý umožňuje čítanie(výstup) obsah vnútorných registrov regulátora;

Ako výstup pre vydá signál na povolenie čítania dáta z JV do pamäte;

● ¯ChtP, ¯ZpP - výstupy pre riadenie čítania z pamäte a zápisu do pamäte;

● ¯VK - vstup (výber kryštálu), na ktorý sa po nastavení signálov zápisu alebo čítania privedie signál výberu nulového čipu. Signál ¯VK inicializuje výmenu dát medzi procesorom a vnútornými registrami ovládača DMA počas programovania; automaticky zablokované v režime priameho prístupu. Vstup ¯VK je pripojený k SHA mikroprocesorového systému priamo alebo cez dekodér.

Závery ¯Zp, ¯Cht sú pripojené k procesoru ako vstupy a k JV ako výstupy a výstupy ¯ZpP, ¯ChtP - k pamäti mikroprocesorového systému.

Na javisku počiatočná inštalácia v generátore adries sa dekódujú bity nižšieho rádu А3…А0 kódu adresy a po prijatí signálov ¯Зп, ¯Тт z procesora sa organizuje zápis alebo čítanie softvérovo prístupných registrov zariadenia DMA. . O pracovať v cykle Logické obvody PDP čítacej a zapisovacej jednotky tvoria na výstupoch zariadenia dvojice signálov ¯Cht, ¯ZpP a ¯Zp, ¯ChtP, ktoré zabezpečujú taktovanie procesu výmeny dát medzi JV a pamäťou.

Ovládací blok

reguluje postupnosť operácií počas všetkých cyklov RAP pomocou riadiacich signálov a tiež prevádza ovládač z pohotovostného stavu do servisného podľa signálu potvrdenia zachytenia (PCx). Riadiaca jednotka má nasledujúce výstupy:

- ЗЗх (Н RQ) - výstup, z ktorého sa prijíma signál žiadosť o zachytenie pre mikroprocesor;

- ПЗх (HLDA) - vstup, na ktorý sa prijíma signál potvrdenie zachytenia z mikroprocesora;

- Гт (RDY) - riadiaci vstup pripravenosť. Signál Гт = 1 z JV aktivuje činnosť regulátora PDP; signál Гт = 0 uvedie regulátor do pohotovostného stavu;

- M128 - výjazd značka cyklu 128: M128 = 1 označuje, že aktuálny cyklus DAP je 128. cyklus od konca dátového poľa;

- KS (TS) - výjazd koniec počítania: CS = 1 označuje WU, že aktuálny cyklus výmeny cez kanál DMA je posledným v prenose dátového poľa. Ak je bit "KS-stop" v registri nastavenia režimu nastavený na 1, kanál bude zakázaný. Výstup CS sa aktivuje (CS = 1), keď je obsah 14-bitového registra počtu cyklov v tomto kanáli nastavený na 0;

- RA (AE) - výstup povolenia adresy: PA = 1 signalizuje systému, že prebiehajú cykly priameho prístupu. V tomto prípade sú všetky zbernice odpojené od mikroprocesora. Signál možno použiť na zablokovanie adresovej zbernice v zariadeniach, ktoré sa nezúčastňujú priameho prístupu, ako aj na zapísanie horných ôsmich bitov kódu adresy do registra vyrovnávacej pamäte adresy a deaktiváciu obvodu na vyzdvihnutie zariadenia. V režime PDP sa vzorkovanie zariadenia vykonáva pomocou signálov ¯PPDP0 – ¯PPDP3;

- STA (STBA) - výjazd stroboskop adresy, signál, ktorého impulzom je vysoký bajt adresy pamäte, prenášaný cez krokový motor do prídavnej vyrovnávacej pamäte údajov. Cez túto vyrovnávaciu pamäť vstupuje vysoký bajt adresy do adresovej zbernice mikroprocesorového systému;

- TI - vstup pre hodinové impulzy;

- Reset - vstup počiatočnej inštalácie zariadenia. Privedením jediného signálu na tento vstup sa vynuluje obsah všetkých softvérovo prístupných registrov, čo vedie k odpojeniu kanálov K0 - K3.

Dátová vyrovnávacia pamäť je 8-bitová obojsmerná trojstavová zbernica, ktorá spája ovládač DMA so systémovou dátovou zbernicou krokového motora.

Cez dátovú vyrovnávaciu pamäť:

- pri programovanie v režime zápisu sa osem dátových bitov D 7 ... D 0 z mikroprocesora prenesie do PDP regulátora na zápis do registra štartovacej adresy, registra počtu cyklov alebo registra nastavenia režimu; keď procesor číta zo zariadenia s priamym prístupom do pamäti, zobrazí sa obsah registra štartovacích adries, register počtu cyklov a register stavu kanála;

- pri prevádzka kanála DMA na začiatku každého cyklu sa horných osem bitov adresy prenesie z registra adries príslušného kanálu do pamäte. Potom sa SD uvoľní na priamu výmenu dát medzi pamäťou a JV počas zvyšku cyklu. Tieto údaje neprechádzajú cez zariadenie PDP.

Nastavenie registra

modes uchováva informácie o naprogramovaných režimoch autoload, rozšírenom a pravidelnom nahrávaní, pevnej priorite a cyklickom posune priorít, KS-stop, atď. Pri programovaní DMA kontroléra sa do neho zapisuje 8-bitové riadiace slovo. Register nastavenia režimu sa zvyčajne načíta po register adries(RgA) a register cyklov(RgC). Účel bitov registra nastavenia režimu je uvedený v tabuľke. 3.11.1.

Register stavu kanála

označuje, v ktorom zo štyroch kanálov sa proces prenosu poľa skončil. Za týmto účelom sa hodnota signálu KS = 1 konca počtu, ktorý sa objaví na výstupe KS a označuje koniec poľa na príslušnom kanáli, zapíše do bitov nižšieho rádu PC0–. PC3 (príznaky dokončenia služby). Vymenovanie hodností register nastavenia režimu je uvedené v tabuľke. 3.11.2.

Základné stavy a prevádzkové režimy zariadenia.

Hlavné štáty sú počiatočný stav, programovanie, čakanie a údržba.

Počiatočný stav.

Pri vstupe Resetovať jeden signál, na ktorý sa prístroj prepne počiatočnéštát. V tomto stave sú maskované požiadavky všetkých DMA kanálov (P0 = P1 = P2 = P3 = 0), vyrovnávacie obvody zbernice A0 ... A3 sa prenesú do stavu prijímania informácií.

Programovanie.

Schopný programovanie zariadenia, mikroprocesor na dátovej zbernici (SM - D 0 ... D 7) zapisuje počiatočnú adresu, počet cyklov a ďalšie údaje do príslušných registrov, ktorých adresa je nastavená kódom A 3 A 2 A 1 A 0 na autobusoch A0–A3 (tabuľka 3.11. 3). Hlavný bit kódu A3 vám umožňuje rozlíšiť, kedy A3 \u003d 0 - kanálové registre K0…K3; pri A3 = 1 - register nastavenia režimu(funguje len na písanie) a register stavu kanála(funguje len na čítanie). Najmenej významný bit A0 vyberá registre počiatočnej adresy (A0 = 0) a počtu cyklov (A0 = 1). Dve stredné číslice A 2 A 1 označujú počet registrov (alebo kanálov) v binárny kód. Napríklad kód 0101 zodpovedá registru počtu cyklov RFC2 - kanál 2. Registre ovládača DMA sa načítajú alebo sa z nich načítajú informácie, ak mikroprocesor vykoná príkaz na zápis alebo čítanie prístupom k zariadeniu a jeho registrom. Na to potrebuje mikroprocesor vydať príslušné zapisovacie signály ¯Zp alebo prečítať ¯Cht a nastaviť adresu registra v tvare kódu A 3 A 2 A 1 A 0 do systémových adresových zberníc SHA. V tomto čase sa do dátovej zbernice krokového motora privádza potrebná informácia D 7 ... D 0 pre zápis do registrov, alebo sa cez dátovú zbernicu krokového motora načíta informácia z PDP regulátora. Na nastavenie stavu programovania je potrebné použiť aj signál načítania zariadenia ¯VK = 0. Vzhľadom na to, že registre kanálov sú 16-bitové, na ich načítanie alebo načítanie sú potrebné dva cykly inštrukcií programu. IN generátor adries Ovládač má spúšť, ktorá automaticky prepína obvody počas operácie čítania alebo zápisu. Tento spúšťač určuje prístup k hornému alebo nízkemu bajtu registra. Spúšť sa resetuje privedením jediného signálu na vstup resetovať, a tiež vždy, keď sa načíta register nastavenia režimu.

Aby sa zabezpečila správna synchronizácia pri prístupe do kanálových registrov, všetky príkazy musia pochádzať z mikroprocesora v pároch, medzi nimi by nemali byť žiadne medzery.

Očakávanie.

Schopný očakávania riadiaca jednotka prijíma z JV signál požiadavky na príjem cyklu PDP (ZPDP0–ZPDP3) a generuje signál požiadavky na zachytenie (ЗЗх) pre mikroprocesor. V tomto stave sú systémové zbernice riadené mikroprocesorom.

servis.

Po prijatí signálu potvrdenia zachytenia (PZx) z mikroprocesora v prítomnosti signálu požiadavky (ZPDP0 - ZPDP3) z JV regulátor vygeneruje signál potvrdenia požiadavky (¯PPDP0 - ¯PPDP3) pre jednu z JV a prepne do servisný stav. IN V tomto stave sú systémové zbernice riadené radičom a je implementovaný jeden z naprogramovaných režimov DMA:

- spodných 8 bitov adresy pamäte sa posiela na zbernice A0–A3, A4–A7, horných 8 bitov - na dátovú zbernicu krokového motora;

- vytvoria sa zodpovedajúce riadiace signály ¯ChtP a ¯ZpP, ¯Zp a ¯Cht, ktoré umožňujú JV prijímať z pamäťovej bunky alebo prenášať do pamäťovej bunky v jednom cykle dátových bajtov.

V prvom cykle prevádzky zariadenie PMA odošle počiatočnú adresu pamäťovej bunky. V nasledujúcich cykloch sa adresa zvyšuje a počet cyklov klesá o jeden, kým sa obsah registra počtu cyklov (alebo skôr jeho 14 bitov) nerovná nule. Potom sa generuje signál koniec počítania Možné sú CS a nasledujúce režimy prevádzky:

- ďalšie zvýšenie adresy pridaním adresy po ďalšom cykle;

- zablokovanie kanálu PDP (režim „KS-stop“);

- opakovanie predtým zvoleného poľa adries (režim automatického načítania).

Počas vykonávania cyklov RAP sú možné tri režimy prevádzky:

- režim čítanie, poskytovanie prenosu dát z pamäte do JV;

- režim záznamy, poskytovanie prenosu dát z JV do pamäte;

- režim kontroly. V tomto režime PMA regulátor negeneruje signály ¯ChtP, ¯ZpP, ¯Ch a ¯Zp, čo bráni výmene dát medzi pamäťou a JV. V každom cykle však ovládač PMA riadi systémovú zbernicu a potvrdzuje požiadavky JV. Externé zariadenia môže použiť potvrdzovacie signály na umožnenie interného prístupu ku každému bajtu v dátovom poli s cieľom vykonať nejakú overovaciu operáciu. Pole kontrolných cyklov môže nasledovať po rade čítacích cyklov, aby umožnilo RT skontrolovať novo prijaté dáta.

Embedded Flash Controller (EFC) je súčasťou Memory Controller (MC) a poskytuje rozhranie na prístup k blokom flash pamäte cez internú 32-bitovú zbernicu. To umožňuje výrazne zvýšiť rýchlosť načítavania inštrukcií z flash pamäte, keď jadro procesora pracuje v režime Thumb (16-bitový inštrukčný systém) vďaka činnosti 32-bitovej vyrovnávacej pamäte. A čo viac, vstavaný ovládač blesku podporuje celá sada príkazy na čítanie, zápis, vymazanie flash pamäte, nastavenie a vymazanie bezpečnostných bitov.

20.2 Popis funkcie

20.2.1 Organizácia vstavanej flash pamäte

Rozhrania internej flash pamäte sú priamo pripojené k internej 32-bitovej zbernici založenej na niekoľkých z nasledujúcich rozhraní.

- Jednoduchá organizácia pamäte: viacero strán rovnakej veľkosti.

- Dve 32-bitové vyrovnávacie pamäte na čítanie určené na zvýšenie rýchlosti čítania flash (pozrite „Príkazy čítania“ na strane 101).

- Jedna zapisovacia vyrovnávacia pamäť na ukladanie údajov pri programovaní jednej flash stránky. Táto vyrovnávacia pamäť má veľkosť jednej stránky a je určená len na zápis. Okrem toho vyrovnávacia pamäť pre zápis adresuje celú oblasť 1 MB flash pamäte (pozrite „Príkazy zápisu“ na strane 101).

- Niekoľko bezpečnostných bitov (uzamykacích bitov) na zabránenie vymazania a zápisu do pamäte flash. Každá chránená oblasť flash pamäte (všetky oblasti majú rovnakú veľkosť) pozostáva z pevného počtu stránok umiestnených za sebou. Každá takáto oblasť je priamo spojená iba s jedným bezpečnostným bitom.

- Niekoľko bitov energeticky nezávislej pamäte - bity NVM (Non Volatile Memory) na všeobecné účely. Každý z týchto bitov je zodpovedný za riadenie určitých uzlov mikrokontroléra. Pre viac detailné informácie pre každý bit NVM si pozrite príslušné kapitoly tohto dokumentu.

Tabuľka 20-1. Počet bezpečnostných bitov a univerzálny bit NVM pre členov rodiny AT91SAM7S

Obrázok 20-1. Vstavaná mapa flash pamäte

20.2.2 Čítanie príkazov

Na urýchlenie procesu čítania flash pamäte je v radiči EFC zabudovaná vyhradená 32-bitová vyrovnávacia pamäť. Vďaka prítomnosti tejto vyrovnávacej pamäte, keď procesor pracuje v režime Thumb (16-bitová inštrukčná sada), dochádza k prístupu k flash pamäti dvakrát zriedkavejšie, vďaka čomu sa zvyšuje rýchlosť načítania inštrukcie a následne aj rýchlosť procesora (obr. 20-2, obr. 20-3 a obr. 20-4).

Táto optimalizácia sa vykonáva iba pri načítavaní inštrukcií a nie pri čítaní údajov z pamäte flash.

Príkazy na čítanie je možné vykonávať s ďalšími čakacími cyklami alebo bez nich. V poli FWS (Flash Wait State) registra režimu blesku MC_FMR je možné nastaviť iba tri (vrátane) čakacích cyklov (pozrite „Register režimu blesku“, strana 110). Pri FWS = 0 sa do vstavanej pamäte flash pristupuje v jednom cykle.

Prístup k pamäti Flash je dostupný v 32-bitovej verzii (slovník), 16-bitovej verzii (polslovo) a 8-bitovej verzii.

Keďže veľkosť vstavanej flash pamäte je menšia ako veľkosť mikrokontroléra, ako veľkosť adresného priestoru internej pamäte, ktorá je mu pridelená (1 MB), pamäťový radič implementuje tzv. duplikácia tohto bloku flash pamäte v rámci adresného priestoru, ktorý je mu pridelený. Napríklad pre AT91SAM7S64 je 64KB flash pamäť mapovaná presne 1024/64 = 16-krát v tomto adresnom priestore.

Obrázok 20-2. Optimalizácia pri čítaní príkazového kódu v režime Thumb pre FWS = 0

Obrázok 20-3. Optimalizácia pri čítaní príkazového kódu v režime Thumb pre FWS = 1

Obrázok 20-4. Optimalizácia pri čítaní príkazového kódu v režime Thumb pre FWS = 3

20.2.3 Zápis príkazov

Do oblasti vnútornej pamäte vyhradenej pre vstavanú pamäť flash je možné zapisovať iba prostredníctvom vyhradenej vyrovnávacej pamäte. Pri vykonávaní príkazov na zápis do pamäte flash sa berie do úvahy iba spodných 8 bitov adresy (pretože rozprávame sa pre 32-bitové dáta sa v skutočnosti berie do úvahy najmenej významných 10 bitov adresy). Horných 10 bitov adresy vnútornej oblasti (1 MB) vyhradenej pre flash pamäť zase adresuje túto tzv. okno s veľkosťou 256 slov (1024 bajtov). Takže toto všetko vnútornú pamäť pozostáva z 1024 takýchto okien.

Akýkoľvek príkaz na zápis do vstavanej pamäte flash môže byť zakázaný jednotkou MPU (Memory Protection Unit).

Do pamäte Flash je možné zapisovať iba slovami (32 bitov), takže akýkoľvek pokus o zápis polovičných slov (16 bitov) alebo bajtov (8 bitov) bude mať nepredvídateľný výsledok.

Príkazy zápisu sa vykonávajú v počte cyklov čakania (pole FWS v MC_FMR) špecifikovanom pre príkazy na čítanie plus jeden cyklus navyše, okrem prípadu, keď FWS = 3 (pozri "Register režimu Flash", strana 110).

20.2.4 Sada príkazov ovládača Flash

EFCS obsahuje príkazy na programovanie flash pamäte, príkazy na nastavenie ochrany (odstránenie ochrany) jej oblastí, príkazy na sekvenčné programovanie a nastavenie ochrany flash pamäte a príkaz na úplné vymazanie celej flash pamäte.

Tabuľka 20-2. Riadiaci systém Flash Controller

Pred vykonaním ktoréhokoľvek z týchto príkazov musí byť pole FCMD registra MC_FCR nastavené na kód pre tento príkaz. Keďže MC_FCR je len na čítanie, príznak FRDY sa automaticky vymaže. Po dokončení vykonávania inštrukcie sa automaticky nastaví príznak FRDY, ktorý môže spustiť príslušné prerušenie, ak je povolené cez pamäťový radič (MC).

Všetky flash inštrukcie sú chránené pred náhodným vykonaním jedným spoločným kľúčovým slovom, ktoré musí byť špecifikované v horných 8 bitoch registra MC_FCR pri každom vykonaní ďalšej inštrukcie.

Inštrukcia s nesprávne špecifikovaným kľúčovým slovom a/alebo nesprávne špecifikovaným kódom pre túto inštrukciu sa nevykoná, aj keď je nastavený príznak PROGE v registri MC_FSR. Tento príznak sa automaticky vynuluje pri ďalšom čítaní registra MC_FSR.

Pokus o zápis alebo vymazanie stránky umiestnenej v chránenej oblasti nebude mať žiadny vplyv na obsah flash pamäte (v skutočnosti bude tento príkaz ignorovaný), aj keď je nastavený príznak PROGE v registri MC_FSR. Tento príznak sa automaticky vynuluje pri ďalšom čítaní registra MC_FSR.

Obrázok 20-5. Vývojový diagram príkazov

Na správne vykonanie príkazov blesku musí byť pole Čas cyklu v mikrosekundách (FMCN) v registri režimu ovládača blesku (MC_FMR) nastavené na správnu hodnotu (pozrite „Register režimu ovládača pamäte Flash“, strana 110).

20.2.4.1 Flash programovanie

Na programovanie flash pamäte je možné použiť len niekoľko príkazov.

Podľa technológie flash pamäte musí byť vymazaná bezprostredne pred procesom jej programovania. Buď celú oblasť flash alebo jednotlivú stránku možno vymazať vymazaním príznaku NEBP v registri MC_FMR priamo zapísaním kódu inštrukcie do registra MC_FCR.

Nastavením príznaku NEBP v registri MC_FMR je možné stránku naprogramovať v určitom počte krokov, ak už bola predtým vymazaná (pozri obrázok 20-6).

Obrázok 20-6. Príklad programovania sekcie stránky Flash

Po ukončení procesu programovania môže byť stránka chránená pred náhodným alebo úmyselným vymazaním alebo zápisom (keď je chránená celá oblasť obsahujúca túto stránku). Pomocou príkazu WPL je možné ochranu nastaviť automaticky ihneď po ukončení cyklu zápisu stránky.

Zapisované dáta sa ukladajú do internej vyrovnávacej pamäte, ktorej veľkosť sa rovná veľkosti jednej flash stránky. Tento interný buffer pokrýva celý adresný priestor interného flashu, t.j. v skutočnosti môže byť zobrazený celý na ktorejkoľvek z jeho stránok.

Poznámka: zapisovanie bajtov (8 bitov) alebo polovičných slov (16 bitov) je zakázané, pretože pretože to spôsobuje poškodenie zaznamenaných údajov.

Proces zápisu dát do flash pamäte, ktorá bola predtým pridelená vo vnútornej vyrovnávacej pamäti, je riadený registrom príkazov flash (MC_FCR). Nižšie je uvedená postupnosť práce s týmto registrom.

- Zápis celej stránky, ktorú možno umiestniť na ľubovoľnú adresu v rámci celého priestoru flash adries, je možný len ako slovník (32-bitové dáta).

- Cyklus zápisu stránky začína ihneď po zadaní čísla stránky a samotného kódu príkazu zápisu v registri MC_FCR. Tým sa automaticky vymaže príznak FRDY v registri stavu programovania Flash (MC_FSR).

- Ihneď po dokončení programovacieho cyklu sa v registri stavu programovania Flash (MC_FSR) nastaví príznak FRDY. Ak sú povolené prerušenia z príznaku FRDY, potom sa v radiči pamäte (MC) vyskytne príslušný signál prerušenia.

- Programming Error: Do registra MC_FSR bola zapísaná neplatná hodnota. kľúčové slovo a/alebo bol zadaný neplatný príkaz.

20.2.4.2 Príkaz úplného vymazania Flash

Všetka flash pamäť na čipe môže byť vymazaná, ak je register MC_FCR zapísaný príkazom "Erase All" - EA (Erase All).

Vymazanie celej flash pamäte je možné len vtedy, keď žiadna z jej oblastí nie je chránená pred vymazaním a zápisom (nie je nastavený ani jeden z príznakov ochrany flash pamäte). V opačnom prípade (je nastavený aspoň jeden príznak ochrany) bude tento príkaz ignorovaný. Ak je nastavený príznak LOCKE v registri MC_FMR, dôjde k zodpovedajúcemu signálu prerušenia.

Príznak FRDY sa automaticky nastaví v registri MC_FSR po vymazaní posledného programovacieho príkazu alebo flash pamäte. V tomto prípade sa zodpovedajúci signál prerušenia okamžite objaví na výstupe pamäťového radiča (MC), ak je povolený.

Počas vykonávania programovacieho cyklu sa môžu vyskytnúť chyby, ktoré sú zaznamenané v registri MC_FSR. Tieto chyby sú uvedené nižšie.

- Programming Error: Do registra MC_FSR bolo zapísané neplatné kľúčové slovo a/alebo bol zadaný neplatný príkaz.

- Chyba uzamknutia: Uskutočnil sa pokus naprogramovať zabezpečenú oblasť. Pre správne naprogramovanie tejto oblasti je potrebné ju najprv odblokovať príkazom unprotect.

20.2.4.3 Ochranné bity Flash

Každý z bezpečnostných bitov je viazaný na konkrétnu oblasť flash pamäte, ktorá pozostáva z určitého počtu stránok. Účelom týchto bitov je chrániť pamäť flash pred náhodným alebo úmyselným vymazaním/programovaním.

Počas výrobného procesu mikrokontroléra môžu byť v ňom nastavené niektoré ochranné bity. Ich účelom je chrániť určitú oblasť flash pamäte, ktorá štandardne obsahuje program zapísaný do mikrokontroléra pri jeho výrobe. Pred naprogramovaním/vymazaním chránenej oblasti musí byť odblokovaná.

Nasleduje poradie, v ktorom je nastavená ochrana pre jednu oblasť:

Do registra príkazov flash by sa mala zapísať nasledujúca hodnota: (0x5A, po vykonaní príkazu ochrany sa nastaví príznak FRDY v registri MC_FSR. To okamžite spôsobí zodpovedajúci signál prerušenia na výstup pamäťového radiča ( MC), ak je povolená. ul>

Po nastavení ochrany je možné ochranu zrušiť, nasledovná postupnosť odblokovania jednej oblasti:

- do registra príkazov flash by sa mala zapísať hodnota: (0x5A po dokončení ochranného príkazu sa nastaví príznak FRDY v registri MC_FSR. V tomto prípade sa na výstupe pamäte okamžite objaví príslušný signál prerušenia ovládač (MC), ak je povolený.

Ak sa pri vykonávaní príkazu vyskytne chyba (v registri MC_FCR je zadané neplatné kľúčové slovo a/alebo nesprávny kód príkazu), tak sa táto skutočnosť zaznamená do registra MC_FSR.

Vykonaním príkazu na vymazanie blokovacieho bitu sa fyzicky zapíše "1" do zodpovedajúceho bitu, hoci čítanie registra MC_FSR prečíta zodpovedajúci bit LOCKx ako "0". Naopak, vykonanie príkazu na nastavenie bitov zámku fyzicky zapíše "0" do zodpovedajúceho bitu a čítanie registra MC_FSR prečíta zodpovedajúci bit LOCKx ako "1".

Poznámka: Bez ohľadu na to, či je pamäť flash chránená, je stále prístupná čítaním.

20.2.4.4 Bity NVM na všeobecné použitie

Bity na všeobecné použitie - NVM bity - nie sú spojené so vstavanou pamäťou flash, ale sú určené na ochranu ostatných uzlov mikrokontroléra. Každý z týchto bitov je možné nastaviť (vymazať) nezávisle od ostatných. Podrobnosti o bitoch NVM nájdete v príslušných kapitolách tohto dokumentu.

Nasleduje aktivačná sekvencia pre univerzálne bity NVM.

- Vykonanie príkazu Set General Purpose NVM Bit (SGPB) zapísaním kódu tohto príkazu a počtu týchto bitov do registra príkazov Flash pamäte (MC_FCR) v poli PAGEN toho istého registra.

- po dokončení inštrukcie SGPB sa nastaví príznak FRDY v registri MC_FSR. V tomto prípade sa zodpovedajúci signál prerušenia okamžite objaví na výstupe pamäťového radiča (MC), ak je povolený.

Počas vykonávania programovacieho cyklu sa môžu vyskytnúť chyby, ktoré sú zaznamenané v registri MC_FSR. Tieto chyby sú uvedené nižšie.

- Pole PAGEN registra MC_FCR označuje počet univerzálnych bitov, ktorý je väčší ako maximálny povolený počet bitov NVM implementovaných v čipe. Nasleduje postupnosť vymazania bitov NVM na všeobecné použitie.

- Vykonanie príkazu Clear General Purpose NVM Bit (CGPB) zapísaním kódu príkazu a počtu týchto bitov do registra príkazov Flash pamäte (MC_FCR) v poli PAGEN toho istého registra.

- po dokončení inštrukcie CGPB sa nastaví príznak FRDY v registri MC_FSR. V tomto prípade sa zodpovedajúci signál prerušenia okamžite objaví na výstupe pamäťového radiča (MC), ak je povolený.

Počas vykonávania programovacieho cyklu sa môžu vyskytnúť chyby, ktoré sú zaznamenané v registri MC_FSR. Tieto chyby sú uvedené nižšie.

- Programming Error: Do registra MC_FSR bolo zapísané neplatné kľúčové slovo a/alebo bol zadaný neplatný príkaz.

- Pole PAGEN registra MC_FCR označuje počet univerzálnych bitov, ktorý je väčší ako maximálny povolený počet bitov NVM implementovaných v čipe.

Vykonaním príkazu "clear NVM general purpose bits" sa fyzicky zapíše "1" do zodpovedajúceho bitu, hoci čítanie registra MC_FSR prečíta zodpovedajúci bit GPNVMx ako "0". Naopak, vykonanie príkazu "Set General Purpose NVM Bits" fyzicky zapíše "0" do zodpovedajúceho bitu a čítanie registra MC_FSR prečíta zodpovedajúci bit GPNVMx ako "1".

Poznámka: bez ohľadu na stav bitov NVM na všeobecné použitie je pamäť flash vždy čitateľná.

20.2.4.5 Bezpečnostný bit

Tajný bit má zabrániť externým pokusom o prístup k internej systémovej zbernici. Po nastavení bezpečnostného bitu sa prevádzkuje rozhranie JTAG, rozhranie rýchleho programovania pamäte flash a prístup do pamäte flash cez sériové rozhranie. Prístup k flash pamäti cez vyššie uvedené rozhrania je opäť povolený len vtedy kompletné čistenie kryštál na externom kolíku ERASE - pozri kapitolu 4. Priradenie kolíkov. Keď je kolík ERASE nastavený na vysokú úroveň (pozrite si časť 7.4. "Vymazať kontrolný kolík"), všetky blesky na čipe, všetky bity ochrany pred bleskom a všetky bity NVM na všeobecné použitie sa vymažú a až po tom všetkom sa vymaže bit súkromia .

Postup nastavenia bitu súkromia je uvedený nižšie.

- Vykonajte príkaz Set Security Bit (SSB) zapísaním kódu príkazu do registra príkazov Flash (MC_FCR).

- po dokončení inštrukcie SSB sa nastaví príznak FRDY v registri MC_FSR. V tomto prípade sa zodpovedajúci signál prerušenia okamžite objaví na výstupe pamäťového radiča (MC), ak je povolený.

Ihneď po nastavení bezpečnostného bitu sa v registri MC_FSR nastaví príznak SECURITY.

sushiandbox.ru Mastering PC - Internet. Skype. Sociálne médiá. Lekcie o Windowse.

sushiandbox.ru Mastering PC - Internet. Skype. Sociálne médiá. Lekcie o Windowse.