Nous avons considéré un décodeur à un étage (linéaire) - c'est le plus rapide, mais sa mise en œuvre avec une largeur de mot d'entrée importante est difficile, car elle nécessite l'utilisation d'éléments logiques avec un grand nombre d'entrées, ce qui s'accompagne d'une charge importante sur les sources de signal d'entrée. En règle générale, les décodeurs à un étage sont réalisés pour un petit nombre d'entrées, déterminé par les capacités des éléments de la série de microcircuits appliquée. Par conséquent, souvent le nombre de sorties du décodeur n'est pas suffisant pour sélectionner quantité requise dispositifs à microprocesseur. En utilisant deux décodeurs avec une entrée de validation E, il est possible de réaliser un décodeur avec le nombre de sorties N = 2 n+1 (Fig. 2.11.3).

Riz. 2.11.3. Décodeur 3x8 basé sur deux décodeurs 2x4

Sur la fig. 2.11.3 montre un schéma d'un décodeur 3x8 combiné implémenté sur deux décodeurs 2x4 complets. Ainsi, il est possible de créer un décodeur 4x16 à partir de 2 décodeurs 3x8, etc. L'entrée de validation E est utilisée comme bit d'adresse. Lorsque E = 0, le décodeur supérieur fonctionne, lorsque E = 1, le décodeur inférieur fonctionne, tandis que toutes les sorties du décodeur supérieur sont à 0.

La méthode en cascade (pyramidale) de construction de décodeurs avec un grand nombre de sorties sur des microcircuits décodeurs avec un plus petit nombre de sorties est également largement utilisée (Fig. 2.11.4).

Pour activer le fonctionnement de l'un des décodeurs 3x8 (DC2, DC3, DC4, DC5), un signal d'activation ou de désactivation est fourni à l'entrée E de chaque décodeur à partir du décodeur DC1 (premier étage), qui est commandé par les bits d'adresse A3 , A4.

Riz. 2.11.4. Schéma d'inclusion en cascade (pyramidale) des décodeurs

Les bits d'adresse A0, A1, A2 sont alimentés en parallèle aux décodeurs du 2ème étage. Le nombre total de bits d'adresse a augmenté de 2 bits.

Encodeurs. Les encodeurs sont des dispositifs conçus pour convertir un code unitaire en binaire. A la sortie du codeur, apparaît un code binaire multi-bits correspondant au nombre décimal de l'entrée à laquelle est appliqué le niveau logique actif. Les encodeurs binaires effectuent l'opération inverse des décodeurs.

L'encodeur est parfois appelé "codeur" (du codeur anglais) et sert, par exemple, à convertir des nombres décimaux tapés sur le clavier d'un panneau de commande à bouton-poussoir en nombres binaires. Si le nombre d'entrées est si grand que le codeur utilise toutes les combinaisons possibles de signaux de sortie, alors un tel codeur est dit complet. Le nombre d'entrées et de sorties dans un codeur complet est lié par la relation N = 2 n , où N est le nombre d'entrées, n est le nombre de sorties. Ainsi, pour convertir le code du clavier en un nombre binaire à quatre chiffres, il suffit d'utiliser seulement 10 entrées, alors que le nombre total d'entrées possibles sera de 16 (n = 2 4 = 16), donc l'encodeur 10x4 sera incomplet .

Considérons un exemple de construction d'un codeur pour convertir un code unitaire à dix bits (nombres décimaux de 0 à 9) en un code binaire. Dans ce cas, on suppose que le signal correspondant à une unité logique n'est appliqué qu'à une seule entrée à la fois.

La table de vérité du codeur est donnée dans le tableau 2.11.3.

Utilisant cette table, nous écrivons des expressions logiques pour les variables de sortie, incluant dans la somme logique les variables d'entrée qui correspondent à l'unité de la variable de sortie correspondante.

Table de vérité du décodeur

Tableau 2.11.3.

| Contributions | Les sorties | |||||||||||||

| № | X0 | X1 | X2 | X3 | X4 | X5 | X6 | X7 | X8 | X9 | A3 | A2 | A1 | A0 |

Écrivons les équations logiques pour les variables de sortie A0, A1, A2, A3 :

A0 = X1 v X3 v X5 v X7 v X9

A1 = X2 contre X3 contre X6 contre X7

A2 = X4 contre X5 contre X6 contre X7

Pour un tel codeur, il est facile de construire un circuit sur des éléments logiques "OU" (Fig. 2.11.5).

Riz. 2.11.5. Schéma d'un encodeur incomplet 10x4

Instructions méthodologiques pour l'exécution des travaux:

Notez dans le rapport, comme d'habitude, le nom du travail, le but du travail. Donnez la définition d'un décodeur. Faites une table de vérité pour un décodeur qui a 3 entrées d'adresse. Notez les équations pour chacune des 8 sorties du décodeur. Construire un diagramme. Construisez un circuit qui implémente les fonctions du décodeur dans Multisim. Découvrez son travail.

Découvrez le fonctionnement de la puce de décodage 2x4. Assemblez le circuit décodeur illustré à la fig. 2.11.4 en utilisant uniquement des décodeurs 2x4.

Obtenez des diagrammes de synchronisation du fonctionnement du circuit. Pour afficher tous les signaux d'entrée et de sortie du décodeur, utilisez 2 analyseurs.

Dessinez un schéma et expliquez son fonctionnement dans le rapport. Veuillez fournir des chronogrammes. Les chronogrammes doivent figurer sur une page, les chronogrammes ne peuvent pas être poursuivis sur une autre page. Toutes les connexions entre les signaux doivent être claires.

Créez une table de vérité pour l'encodeur 8x3 complet. Écrivez les fonctions logiques des variables de sortie. Construisez et recherchez le circuit du brouilleur. Dans le rapport, fournir une table de vérité, des équations, un schéma construit d'après des équations, des chronogrammes.

Notez les conclusions correspondant à chaque élément du travail effectué.

Questions à préparer pour le rapport :

1. Définissez un décodeur.

2. Définissez un brouilleur.

3. Qu'entend-on par code unitaire ?

4. Quelle est la différence entre un décodeur complet et un décodeur incomplet ?

5. Quelle est la différence entre un encodeur complet et incomplet ?

6. Quelle est la différence entre un décodeur linéaire et un décodeur pyramidal ?

7. Un décodeur linéaire ou un décodeur pyramidal a-t-il plus de vitesse ?

8. Des coûts matériels supplémentaires sont nécessaires pour mettre en œuvre un décodeur linéaire ou pyramidal ?

9. Pourquoi les décodeurs et les encodeurs sont-ils utilisés en informatique ?

12. Travaux de laboratoire n° 12

Recherche de multiplexeurs et démultiplexeurs

Objectif:Étudier les principes de synthèse et de fonctionnement des multiplexeurs et démultiplexeurs.

Exercer: Synthétisez le circuit multiplexeur, étudiez le fonctionnement du circuit. Explorez la puce du multiplexeur, construisez et étudiez le fonctionnement du circuit pyramidal. Synthétisez le circuit démultiplexeur, étudiez le fonctionnement du circuit. Rechercher travail conjoint multiplexeur et démultiplexeur.

Introduction théorique

Multiplexeur est appelé un dispositif logique combinatoire conçu pour la transmission contrôlée de données provenant de plusieurs sources d'informations dans un canal de sortie. Les entrées du multiplexeur sont divisées en informations ré 0 , ré 1 , ...... et commande (adresse) MAIS 0 , MAIS 1 , …, MAIS n-1 .

Le code appliqué aux entrées d'adresse détermine laquelle des entrées d'information est en cours de transfert vers la sortie du circuit. Parce que le n le code binaire -bit peut prendre 2 n valeurs, alors si le nombre d'entrées d'adresse du multiplexeur est n, le nombre de ses entrées d'information doit être égal à 2 n .

Construisons une table de vérité qui affiche le fonctionnement d'un multiplexeur avec deux entrées d'adresse en fonction de la définition. Notons dans le tableau A0 et A1 - entrées d'adresse. D0, D1, D2, D3 - entrées de 4 flux de données, lors du réglage de l'adresse, les données correspondantes seront transmises à la sortie unique du multiplexeur Y (tableau 2.12. 1).

Le tableau ressemble à ceci :

Tableau 2.12. une

| Adresse | Données | Sortir | ||||

| A1 | A0 | D0 | D1 | D2 | D3 | Oui |

| D0 | D1 | D2 | D3 | D0 | ||

| D0 | D1 | D2 | D3 | D1 | ||

| D0 | D1 | D2 | D3 | D2 | ||

| D0 | D1 | D2 | D3 | D3 |

Écrivons l'équation de la fonction Y :

Y = A1*A0*D0 v A1*A0 D1 v A1 A0*D2 v A1 A0 D3.

Le circuit qui implémente la fonction Y peut être construit sur 2 inverseurs, 4 éléments "ET" à trois entrées et un élément "OU" à quatre entrées (Fig. 12.2.1).

Riz. 12.2.1. Circuit multiplexeur 4-1

Il est possible d'assembler un décodeur pour mettre en œuvre le même circuit et l'utiliser pour commuter les entrées sur la sortie Y (Fig. 2.12.2).

Riz. 2.12.2. Circuit multiplexeur et son symbole

Dans les cas où la fonctionnalité des circuits intégrés multiplexeurs ne satisfait pas les développeurs en termes de nombre d'entrées d'informations, ils ont recours à leur mise en cascade afin d'augmenter le nombre d'entrées à la valeur requise. La manière la plus universelle d'augmenter la dimension d'un multiplexeur est de construire une structure pyramidale composée de plusieurs multiplexeurs. Dans ce cas, le premier étage du circuit est une colonne contenant autant de multiplexeurs que nécessaire pour obtenir le nombre requis d'entrées d'informations. Tous les multiplexeurs de cette colonne sont commutés par le même code d'adresse, composé du nombre correspondant de chiffres les moins significatifs du code d'adresse commun. Les chiffres supérieurs du code d'adresse sont utilisés dans le second étage dont le multiplexeur assure le fonctionnement alterné des multiplexeurs du premier étage vers une sortie commune. Le circuit en cascade du multiplexeur "16-1", construit sur les multiplexeurs "4-1", est illustré à la fig. 2.12.3.

Riz. 2.12.3. Multiplexeur en cascade 16-1

Une application typique d'un multiplexeur est la transmission d'informations provenant de plusieurs sources d'informations spatialement séparées (capteurs) à l'entrée d'un récepteur.

Supposons que la température est mesurée environnement dans plusieurs pièces et les résultats de ces mesures doivent être saisis dans un seul appareil d'enregistrement, tel qu'un ordinateur. En même temps, comme la température change lentement, il n'est pas nécessaire de la mesurer constamment pour obtenir une précision suffisante. Il suffit d'avoir des informations à certains intervalles fixes.

Le multiplexeur remplit la fonction de connecter diverses sources d'informations à un récepteur à une commande donnée.

Le multiplexeur peut être utilisé comme élément logique universel pour mettre en oeuvre toute fonction logique à partir du nombre d'arguments égal au nombre d'entrées d'adresse du multiplexeur. Montrons cela sur l'exemple d'une fonction logique donnée par une table de vérité (tableau 2.12.2).

Tableau 2.12.2

| № | A2 | A1 | A0 | Oui | № | A2 | A1 | A0 | Oui |

Schéma qui met en œuvre cette fonction illustré à la fig. 2.12.4.

Riz. 2.12.4. Réalisation d'un circuit combinatoire à l'aide d'un multiplexeur

Démultiplexeur- il s'agit d'un circuit combinatoire avec une entrée d'information (D), n entrées de commande (adresse) (A0, A1, ..., An-1) et N = 2 n sorties (Y0, Y1, ..., YN- 1). Le code binaire arrivant sur les entrées d'adresse détermine l'une des N sorties, à laquelle est transmise la valeur de la variable issue de l'entrée d'information D. Le démultiplexeur met en oeuvre une fonction inverse de la fonction de multiplexeur. Il est conçu pour diviser le flux de données d'une source d'information en plusieurs canaux de sortie.

Le tableau de fonctionnement du démultiplexeur (tableau 2.12.2), qui comporte 4 sorties d'information (Y0, Y1, Y2, Y3) et n = 2 entrées d'adresse (A0, A1), est présenté ci-dessous.

Tableau 2.12.2

| Saisie d'informations | Adresse | Points d'information | ||||

| ré | A1 | A0 | Y0 | Y1 | Y2 | Y3 |

| ré | ré | |||||

| ré | ré | |||||

| ré | ré | |||||

| ré | ré |

Equations décrivant le fonctionnement du démultiplexeur :

Y0 = D A1* A0* ; Y1 = D A1*A0 ; Y2 = A1 A0* ; Y3 = A1 A0.

Le schéma du démultiplexeur construit selon ces équations et sa représentation graphique sont illustrés à la fig. 2.12.5.

Riz. 2.12.5. Schéma du démultiplexeur "1-4" et son image conditionnelle

La fonction de démultiplexeur est facilement mise en œuvre à l'aide d'un décodeur, si son entrée "Enable" - E est utilisée comme entrée d'information du démultiplexeur, et les entrées 1, 2, 4 ... - comme entrées d'adresse du démultiplexeur A0, A1, A2 , ... En effet, avec la valeur active du signal à l'entrée E, la sortie correspondant au code appliqué aux entrées d'adresse est sélectionnée. Par conséquent, les circuits intégrés de décodeurs avec une entrée de validation sont parfois appelés non seulement décodeurs, mais décodeurs-démultiplexeurs.

Le terme "multiplexage" fait référence au processus de transmission de données à partir de plusieurs sources sur un canal commun. Un multiplexeur est utilisé comme un dispositif qui effectue l'opération de réduction des données en un seul canal du côté émission. Un tel dispositif est capable de séparer temporellement des signaux provenant de plusieurs sources et de les transmettre au canal (ligne) de communication les uns après les autres en fonction du changement de codes à ses entrées d'adresse.

Du côté réception, il est généralement nécessaire d'effectuer l'opération inverse - démultiplexage, c'est-à-dire répartition des portions de données reçues sur le canal de communication à des instants successifs, selon leurs récepteurs. Cette opération est effectuée par le démultiplexeur. Partage du multiplexeur et du démultiplexeur pour transférer les données de 4 sources vers

4 récepteurs sur une ligne commune est illustré à la fig. 2.12.6.

Riz. 2.12.6. Partage du multiplexeur et du démultiplexeur pour la transmission de données

Informations similaires.

Les titulaires du brevet RU 2559705 :

L'invention concerne le domaine de l'informatique, de l'automatisation et peut être utilisée dans diverses structures et systèmes numériques contrôle automatique, transfert d'informations, etc.

Dans divers systèmes de calcul et de contrôle, les décodeurs sont largement utilisés, implémentés sur la base d'une logique transistor-transistor et couplée à un émetteur, fonctionnant selon les lois de l'algèbre booléenne et ayant deux états logiques "0" et "1" en sortie, caractérisée par des potentiels faibles et élevés. L'architecture classique du décodeur a été publiée dans des articles et des livres, les micropuces sont produites en série.

Un inconvénient important de cette classe de décodeurs est que ses éléments logiques, utilisant des signaux binaires potentiels, ont une structure à plusieurs niveaux impossible ou inefficace à utiliser dans les processus techniques modernes à basse tension, ainsi que la non-linéarité des modes de fonctionnement de les éléments et la criticité des paramètres de la structure des éléments logiques et des signaux d'entrée. A terme, cela conduit à une diminution des performances des décodeurs connus.

En tant que dispositifs de traitement d'informations numériques, on utilise également des cascades de transistors pour convertir des variables logiques d'entrée (courants), implémentées sur la base de miroirs de courant qui implémentent la fonction de traitement logique des variables de courant d'entrée.

Un inconvénient important des circuits connus de cette classe est qu'ils n'implémentent pas la fonction de conversion de deux signaux de courant d'entrée ayant quatre états "00", "01", "10", "11" en quatre signaux de courant de sortie. Ceci ne permet pas de créer sur sa base une base complète d'outils de traitement du signal à variables courantes fonctionnant sur les principes de l'algèbre linéaire.

Dans les travaux, ainsi que dans les monographies du co-auteur de cette demande, il est montré que l'algèbre booléenne est un cas particulier d'une algèbre linéaire plus générale, dont la mise en œuvre pratique dans la structure des dispositifs informatiques et logiques d'un nouveau la génération d'automatisation nécessite la création d'une base d'éléments spéciale, mise en œuvre sur la base d'une logique avec des signaux de représentation internes à deux et plusieurs valeurs, dans laquelle l'équivalent du signal logique standard est le quantum de courant Ι 0 . Le dispositif revendiqué "Décodeur 2 à 4" fait référence à ce type de dispositifs logiques et fonctionne avec des signaux de courant d'entrée et génère un signal de courant de sortie.

Le prototype le plus proche de l'appareil revendiqué est l'appareil logique "Decoder 2 to 4", présenté dans le brevet US 5742154, contenant les première 1 et deuxième 2 entrées logiques de l'appareil, la première 3, la deuxième 4, la troisième 5, la quatrième 6 sorties logiques de courant du dispositif, les premier 7, deuxième 8 et troisième 9 transistors de sortie, dont les bases sont combinées et connectées à la première 10 source de tension de polarisation, les quatrième 11, cinquième 12 et sixième 13 transistors de sortie de un type de conductivité différent, dont les bases sont combinées et connectées à la deuxième source de tension de polarisation 14, l'émetteur du premier transistor de sortie 7 connecté à l'émetteur du quatrième transistor de sortie 11, l'émetteur du deuxième transistor de sortie 8 est connecté à l'émetteur du cinquième transistor 12 sorties, l'émetteur du troisième transistor 9 sorties est connecté à l'émetteur du sixième transistor 13 sorties, la première sortie logique 3 courant de l'appareil est connectée au collecteur de la première 7 sorties transistor, le deuxième 4 dispositifs de sortie logique de courant a est relié au collecteur du troisième transistor de sortie 9, le collecteur du quatrième transistor de sortie 11 est relié à la troisième sortie logique 5 courant du dispositif, le collecteur du sixième transistor de sortie 13 est relié au quatrième transistor 6 courant de sortie sortie du dispositif, les premier 15 et deuxième 16 miroirs de courant appariés au premier bus 17 d'alimentation, le troisième miroir de courant 18, apparié au deuxième bus 19 d'alimentation, une source auxiliaire de courant de référence 20.

L'objectif principal de l'invention proposée est de créer un élément logique qui assure le décodage de l'état de deux variables logiques d'entrée et la formation de quatre signaux de sortie sous la forme actuelle. En fin de compte, cela vous permet d'augmenter la vitesse des dispositifs de conversion d'informations connus utilisant le décodeur de l'invention et de créer une base d'éléments de dispositifs informatiques fonctionnant sur les principes de l'algèbre linéaire multivaluée.

Le problème est résolu par le fait que dans le dispositif logique "Décodeur 2 à 4" (Fig. 1), contenant les première 1 et deuxième 2 entrées logiques du dispositif, la première 3, la deuxième 4, la troisième 5, la quatrième 6 sorties logiques de courant du dispositif, les premier 7, deuxième 8 et troisième 9 transistors de sortie, dont les bases sont combinées et connectées à la première 10 source de tension de polarisation, les quatrième 11, cinquième 12 et sixième 13 transistors de sortie d'un type de conductivité différent, dont les bases sont combinées et connectées à la deuxième source de tension de polarisation 14, l'émetteur du premier transistor de sortie 7 est connecté à l'émetteur du quatrième transistor de sortie ET, l'émetteur du deuxième transistor de sortie 8 est connecté à l'émetteur du cinquième transistor 12 sorties, l'émetteur du troisième transistor 9 sorties est connecté à l'émetteur du sixième transistor 13 sorties, la première sortie logique 3 courant de l'appareil est connectée au collecteur de la première 7 sorties transistor, la deuxième sortie logique 4 courant de l'appareil est reliée au collecteur de la troisième sortie 9 concernant le transistor, le collecteur du quatrième transistor de sortie 11 est relié à la troisième sortie logique 5 courant du dispositif, le collecteur du sixième transistor de sortie 13 est relié à la quatrième sortie logique 6 courant du dispositif, le premier 15 et deuxième miroir de courant 16, adapté au premier bus d'alimentation 17, troisième miroir de courant 18, adapté au deuxième bus d'alimentation 19, source de courant de référence auxiliaire 20, de nouveaux éléments et connexions sont fournis - la première entrée logique 1 de l'appareil est reliée à l'entrée du troisième 18 miroir de courant, la deuxième 2 entrée logique de l'appareil est reliée à l'entrée du premier 15 miroir de courant, la première 21 la sortie courant du premier 15 miroir de courant est reliée aux émetteurs combinés des deuxième 8 et cinquième 12 transistors de sortie et à travers la source de courant auxiliaire de référence 20 est reliée au deuxième 19 bus d'alimentation, la deuxième sortie de courant 22 du premier 15 miroir de courant est reliée aux émetteurs combinés des premier 7 et quatrième 11 transistors de sortie ov et est relié à la première sortie de courant 23 du troisième miroir de courant 18, le collecteur du deuxième transistor de sortie 8 est relié à l'entrée du deuxième miroir de courant 16 dont la sortie de courant est reliée aux émetteurs combinés du des troisième 9 et sixième 13 transistors de sortie et est relié à la deuxième 24 sortie de courant des troisièmes 18 miroirs de courant, et le collecteur du cinquième 12 transistor de sortie est relié au deuxième bus 19 de la source d'alimentation.

La disposition de l'unité logique prototype est illustrée à la Fig. 1. Sur la Fig. 2 montre un schéma du dispositif revendiqué conformément au paragraphe 1 des revendications.

En figue. 3 montre un schéma du dispositif revendiqué conformément au paragraphe 2, paragraphe 3, paragraphe 4 des revendications.

En figue. 4 est un diagramme schématique de la Fig. 3 dans l'environnement de simulation informatique MS9 avec la mise en œuvre spécifique des principales unités fonctionnelles (miroirs de courant, sources de courant de référence).

En figue. 5 présente les résultats de la simulation informatique du circuit de la Fig. quatre.

Dispositif logique "Décodeur 2 à 4" de la Fig. 2 contient les première 1 et deuxième 2 entrées logiques de l'appareil, les premières 3, les deuxième 4, les troisième 5, les quatrième 6 sorties logiques courant de l'appareil, les premières 7, les deuxième 8 et les troisième 9 transistors de sortie, dont les bases sont combinées et connectées à la première 10 source de tension de polarisation, des quatrième 11, cinquième 12 et sixième 13 transistors de sortie d'un type de conductivité différent, dont les bases sont combinées et connectées à la deuxième 14 source de tension de polarisation, le l'émetteur du premier transistor de sortie 7 est relié à l'émetteur du quatrième transistor de sortie 11, l'émetteur du deuxième transistor de sortie 8 est relié à l'émetteur du cinquième transistor de sortie 12, l'émetteur du troisième transistor de sortie 9 est relié à l'émetteur du sixième transistor 13 sorties, la première sortie logique 3 courants de l'appareil est reliée au collecteur du premier transistor 7 sorties, la deuxième sortie logique 4 courants de l'appareil est reliée au collecteur du troisième transistor 9 sorties , le collecteur du quatrième transistor de sortie 11 est relié au troisième courant 5 lo sortie logique de l'appareil, le collecteur du sixième transistor de sortie 13 est relié à la quatrième sortie logique 6 courant de l'appareil, les premier 15 et deuxième 16 miroirs de courant appariés avec le premier bus d'alimentation 17, le troisième miroir de courant 18 apparié avec le deuxième bus d'alimentation 19, une source auxiliaire de courant de référence 20. La première entrée logique 1 de l'appareil est reliée à l'entrée du troisième miroir de courant 18, la deuxième entrée logique 2 de l'appareil est reliée à l'entrée du premier miroir de courant 15, la première sortie de courant 21 du premier miroir de courant 15 est reliée aux émetteurs combinés des deuxième 8 et cinquième 12 transistors de sortie et à travers la source de courant de référence auxiliaire 20 est reliée au deuxième bus d'alimentation 19, le la deuxième sortie de courant 22 du premier miroir de courant 15 est connectée aux émetteurs combinés des premier 7 et quatrième 11 transistors de sortie et est connectée à la première sortie de courant 23 du troisième miroir de courant 18, le collecteur du deuxième transistor de sortie 8 est connecté à l'entrée la maison du deuxième miroir de courant 16, dont la sortie de courant est connectée aux émetteurs combinés des troisième 9 et sixième transistors de sortie 13 et est connectée à la deuxième sortie de courant 24 du troisième miroir de courant 18, et le collecteur du le cinquième transistor 12 de sortie est relié au deuxième bus 19 d'alimentation.

En figue. 3 conformément au paragraphe 2 des revendications, la première 1 entrée logique du dispositif est reliée à l'entrée du troisième miroir de courant 18 par l'intermédiaire du premier étage inverseur supplémentaire, réalisé sous la forme du premier miroir de courant supplémentaire 26, adapté à les 17 premiers bus d'alimentation.

En figue. 3 conformément au paragraphe 3 des revendications, le collecteur du quatrième transistor de sortie 11 est relié à la troisième sortie logique de courant 5 du dispositif par l'intermédiaire du deuxième étage inverseur supplémentaire, réalisé sous la forme d'un deuxième miroir de courant supplémentaire 27, adapté avec le deuxième bus d'alimentation 19.

De plus, sur la Fig. 3 conformément au paragraphe 4 des revendications, le collecteur du sixième transistor de sortie 13 est relié à la quatrième sortie logique courant 6 du dispositif par l'intermédiaire d'un troisième étage inverseur supplémentaire, réalisé sous la forme d'un troisième miroir de courant supplémentaire 28, adapté avec le deuxième bus d'alimentation 19.

Considérez le fonctionnement du circuit décodeur proposé avec les entrées et sorties de courant de la Fig. 2.

Le décodeur 2 à 4 implémente des fonctions bien connues :

où A 0 , A ¯ 0 - signaux directs et inverses à l'entrée 1 du dispositif de la Fig. 2,

A 1 , A ¯ 1 - signaux directs et inverses à l'entrée 2 du dispositif de la Fig. 2.

Une caractéristique de leur implémentation en algèbre linéaire est l'utilisation de l'opération de différence tronquée à cette fin :

dont la table de vérité est donnée ci-dessous

Il ressort du tableau que sur quatre combinaisons possibles de valeurs de variables d'entrée, une seule valeur de la fonction correspond à une seule combinaison correspondant à la condition A 0 >A 1 . En spécifiant les variables d'entrée directes et inverses dans la table de vérité, on peut obtenir une seule valeur de la fonction correspondant à l'une des combinaisons possibles de valeurs des variables d'entrée.

L'application de cette opération donne la représentation suivante fonctions logiques décodeur :

La mise en oeuvre de ces opérations est la suivante.

Les signaux des variables d'entrée A 0 et A 1 via les entrées logiques 1 et 2 sont fournis aux premier 15 et troisième 18 miroirs de courant, à travers lesquels les signaux spécifiés sont multipliés et leur signe change. Dans ce cas, le signal A 0 est transmis sous la forme d'un courant sortant (c'est-à-dire sous la forme de A 0) et, à l'aide du troisième miroir de courant 18, est converti en un courant entrant (c'est-à-dire sous la forme -A 0), et A 1 se présente sous forme directe sous la forme d'un courant entrant (c'est-à-dire sous la forme de -A 1) et à l'aide du premier miroir de courant 15 est converti en un courant sortant (c'est-à-dire sous la forme de A 1).

Au point de connexion des sorties 22 du premier miroir de courant 15 et 23 du troisième miroir de courant 18, l'opération A 1 -A 0 est mise en oeuvre. Le signal de différence est appliqué aux émetteurs combinés des transistors 7 et 11, dont les modes de fonctionnement sont fixés par les première 10 et deuxième 14 sources de tension de polarisation.

Si le signal de différence est positif, c'est-à-dire A 0 -A 1 >0, le transistor 7 est fermé et le transistor 11 est ouvert et le quantum du courant entrant est délivré à la sortie 5, correspondant à -(A 0 -A 1)=A 1 -A 0 qui implémente l'expression (2). Pour toute autre combinaison de valeurs quantiques de courant, il n'y aura pas de courant à la sortie 5.

Si A 0 -A 1 ≤ 0, alors le transistor 7 est ouvert, et le transistor 11 est fermé et la sortie 3 reçoit un quantum du courant sortant correspondant à A 0 -A 1 qui met en oeuvre l'expression (3). Pour toute autre combinaison de valeurs quantiques de courant, il n'y aura pas de courant à la sortie 3.

Au point de connexion de la sortie 21 du premier miroir de courant et de la source auxiliaire de courant de référence 20, A 1 -1 est soustrait. Le signal de différence est appliqué aux émetteurs combinés des transistors 8 et 12 dont les modes de fonctionnement sont fixés par les première 10 et deuxième 14 sources de tension de polarisation. Si le signal de différence est positif, c'est-à-dire A 1 -1>0, le transistor 8 est fermé, et le transistor 12 est ouvert. Si le signal de différence est inférieur ou égal à zéro, alors le transistor 8 est ouvert et le transistor 12 est fermé.

Dans le premier cas, le signal traversant le transistor 12 se ferme à la masse. Dans le second cas, le quantum du courant différentiel sortant A 1-1 à l'aide du troisième miroir de courant 16 est converti en quantum de courant sortant 1-A 1 et le quantum de courant entrant -A 0 en est soustrait. Le signal de différence est appliqué aux émetteurs combinés des transistors 9 et 13 dont les modes de fonctionnement sont fixés par les première 10 et seconde 14 sources de tension de polarisation. Si le signal de différence est positif, c'est-à-dire le transistor 9 est fermé et le transistor 13 est ouvert. En même temps, un signal de différence (1-A 1)-A 0 est fourni à la sortie 6 sous la forme d'un quantum de courant sortant, qui met en œuvre l'expression (4). Pour toute autre combinaison de valeurs quantiques de courant, il n'y aura pas de courant à la sortie 4.

spécificité cet appareil est la représentation des signaux de sortie sous forme de quanta du courant entrant (aux sorties 3 et 4) et sortant (aux sorties 5 et 6). Pour le cas où tous les signaux de sortie dans le même sens sont nécessaires, le circuit décodeur représenté sur la Fig. 3. Sa différence avec le schéma de la Fig. 2 est l'utilisation de deux miroirs de courant supplémentaires 27 et 28, aux entrées desquels sont connectés les collecteurs des transistors 11 et 13, et les sorties sont les sorties 5 et 6 du décodeur. En conséquence, tous les signaux de sortie sont représentés par des quanta du courant entrant.

Comme il ressort de la description ci-dessus, la mise en œuvre du dispositif « Décodeur 2 à 4 » s'effectue sous la forme de fonctions logiques standards selon les lois de l'algèbre linéaire en formant la différence de quanta de courant 10. La mise en œuvre des éléments sur les miroirs de courant permet dans de nombreux cas de réduire la tension d'alimentation, et puisque tous les éléments des circuits fonctionnent en mode actif, ce qui suppose l'absence de saturation lors de la commutation, les performances globales de l'appareil augmentent. L'utilisation de valeurs stables de quanta de courant I 0 , ainsi que la détermination du signal de sortie par la différence de ces courants, assure une faible dépendance du fonctionnement du circuit aux facteurs de déstabilisation externes (écart de tension d'alimentation, effets de rayonnement et de température , bruit de mode commun, etc.).

Montré à la Fig. 9, fig. 10 résultats de simulation confirment les propriétés spécifiées des circuits proposés.

Ainsi, les solutions de circuit considérées du dispositif logique "Décodeur 2 à 4" sont caractérisées par une représentation en courant binaire du signal et peuvent être utilisées comme base pour des dispositifs de calcul et de contrôle utilisant l'algèbre linéaire, dont un cas particulier est l'algèbre booléenne .

BIBLIOGRAPHIE

1. Brevet US 6243319 B1, fig. 13.

2. Brevet US 5604712 A.

3. Brevet US 4514829 A.

4. Brevet US 20120020179 A1.

5. Brevet US 6920078 B2.

6. Brevet US 6324117 B1, fig. 3.

7. Demande de brevet US 20040018019 A1.

8. Brevet US 5568061 A.

9. Brevet US 5148480 A, fig. quatre.

10. Brzozowski I., Zachara L., Kos A. Universal design method of n-to-2n decoders // Mixed Design of Integrated Circuits and Systems (MIXDES), 2013 Actes de la 20e Conférence internationale, 2013. - P. 279 -284 Fig. une.

11. Subramanyam MV Switching Theory and Logic Design / Firewall Media, 2011. Deuxièmement, - 783 c, Fig. 3.174.

12. SN74LVC1G139 Décodeur de ligne 2 à 4 [ Ressource électronique]. URL : http://www.ti.com/lit/ds/symlink/sn741vc1g139.pdf.

13. Brevet US 8159304, fig. 5.

14. Brevet américain n° 5977829, fig. une.

15. Brevet américain n° 5789982, fig. 2.

16. Brevet américain n° 5140282.

17. Brevet américain n° 6624701, fig. quatre.

18. Brevet américain n° 6529078.

19. Brevet américain n° 5734294.

20. Brevet américain n° 5557220.

21. Brevet américain n° 6624701.

22. Brevet RU n° 2319296.

23. Brevet RU n° 2436224.

24. Brevet RU n° 2319296.

25. Brevet RU n° 2321157.

26. Brevet US 6556075, fig. 2.

27. Brevet US 6556075, fig. 6.

28. Chernov N.I., Yugai V.Y., Prokopenko N.N., et al. Concept de base de la synthèse linéaire des structures numériques à valeurs multiples dans les espaces linéaires // 11e Symposium Est-Ouest sur la conception et les tests (EWDTS 2013). - Rostov-sur-le-Don, 2013. - C. 146-149.

29. Malyugin V.D. Réalisation de fonctions booléennes par des polynômes arithmétiques // Automatisme et Télémécanique, 1982. N° 4. p. 84-93.

30. Tchernov N.I. Principes fondamentaux de la théorie de la synthèse logique des structures numériques sur le corps des nombres réels // Monographie. - Taganrog : TRTU, 2001. - 147 p.

31. Tchernov N.I. Synthèse linéaire des structures numériques ASOIU // Didacticiel. -Taganrog : TRTU, 2004 - 118 p.

1. Décodeur 2 à 4, contenant les première (1) et deuxième (2) entrées logiques de l'appareil, les première (3), deuxième (4), troisième (5), quatrième (6) sorties logiques courantes de l'appareil , les premier (7), deuxième (8) et troisième (9) transistors de sortie dont les bases sont combinées et reliées à la première (10) source de tension de polarisation, les quatrième (11), cinquième (12) et sixième (13) transistors de sortie d'un type de conductivité différent, dont les bases sont combinées et connectées à la deuxième (14) source de tension de polarisation, l'émetteur du premier (7) transistor de sortie est connecté à l'émetteur du quatrième (11 ) transistor de sortie, l'émetteur du second (8) transistor de sortie est connecté à l'émetteur du cinquième (12) transistor de sortie, l'émetteur du troisième (9) transistor de sortie est connecté à l'émetteur du sixième (13) transistor de sortie, la première (3) sortie logique courant du dispositif est reliée au collecteur du premier (7) transistor de sortie, la seconde (4) sortie logique courant du dispositif est reliée au collecteur du troisième (9) transistor de sortie, colle Le facteur du quatrième (11) transistor de sortie est relié à la troisième (5) sortie logique courant du dispositif, le collecteur du sixième (13) transistor de sortie est relié à la quatrième (6) sortie logique courant du dispositif, les premier (15) et deuxième (16) miroirs de courant sont appariés au premier (17) bus d'alimentation, le troisième (18) miroir de courant est apparié au deuxième (19) bus d'alimentation, la source de courant auxiliaire de référence (20) , caractérisé en ce que la première (1) entrée logique du dispositif est reliée à l'entrée du troisième (18) miroir de courant, la seconde (2) entrée logique du dispositif est reliée à l'entrée du premier (15) miroir de courant miroir, la première (21) sortie de courant du premier (15) miroir de courant est connectée aux émetteurs combinés des deuxième (8) et cinquième (12) transistors de sortie et à travers la source de courant de référence auxiliaire (20) est connectée au deuxième (19) bus d'alimentation, la deuxième (22) sortie de courant du premier (15) miroir de courant est connectée aux émetteurs combinés de la première (7) et de la quatrième (11) sortie transistors et est connecté à la première (23) sortie de courant du troisième (18) miroir de courant, le collecteur du second (8) transistor de sortie est connecté à l'entrée du second (16) miroir de courant dont la sortie de courant est connecté aux émetteurs combinés des troisième (9) et sixième (13) transistors de sortie et est connecté à la deuxième (24) sortie de courant du troisième (18) miroir de courant, et au collecteur du cinquième (12) transistor de sortie est relié au second (19) bus d'alimentation.

2. Décodeur 2 à 4 selon la revendication 1, caractérisé en ce que la première (1) entrée logique du dispositif est reliée à l'entrée du troisième (18) miroir de courant par l'intermédiaire du premier étage inverseur supplémentaire, réalisé sous la forme du premier (26) miroir de courant supplémentaire, cohérent avec le premier (17) rail d'alimentation.

3. Décodeur 2 à 4 selon la revendication 1, caractérisé en ce que le collecteur du quatrième (11) transistor de sortie est relié à la troisième (5) sortie logique courant du dispositif par l'intermédiaire d'un deuxième étage inverseur supplémentaire, réalisé sous la forme de un deuxième (27) miroir de courant supplémentaire, adapté au deuxième (19) rail d'alimentation.

4. Décodeur 2 à 4 selon la revendication 1, caractérisé en ce que le collecteur du sixième (13) transistor de sortie est relié à la quatrième (6) sortie logique courant du dispositif par l'intermédiaire d'un troisième étage inverseur supplémentaire, réalisé sous la forme d'un un troisième (28) miroir de courant supplémentaire, adapté au deuxième (19) rail d'alimentation.

Brevets similaires :

Objet : l'invention concerne des moyens de codage utilisant un livre de codes réduit à réinitialisation adaptative. Le résultat technique consiste à réduire la quantité d'informations transmises du côté réception vers le côté émission.

L'invention concerne l'informatique, à savoir l'encodage d'informations vidéo. Le résultat technique consiste à augmenter l'efficacité de codage et de décodage du flux binaire d'informations vidéo en divisant les données en couches d'entropie.

L'invention concerne un procédé de codage d'une séquence d'entiers, un dispositif de stockage et un signal porteur d'une telle séquence codée, ainsi qu'un procédé de décodage de cette séquence codée.

L'invention concerne un procédé de précodage et un système et un procédé de construction d'un livre de codes de précodage dans un système à entrées multiples et sorties multiples (MIMO).

L'invention concerne le domaine de la technologie qui utilise des signaux numérisés et peut être appliquée dans des dispositifs de communication, d'enregistrement, d'enregistrement, de lecture, de conversion, de codage et de compression de signaux, des systèmes de contrôle automatique.

L'invention se rapporte au domaine des télécommunications, à savoir au domaine des dispositifs et procédés cryptographiques de vérification des signature numérique(EDS). .

L'invention concerne le domaine du traitement numérique du signal, notamment la compression de données et l'amélioration du codage entropique de séquences vidéo. Le résultat technique est d'augmenter l'efficacité et de réduire complexité de calcul codage entropique. Un procédé de traitement d'un flux de données constitué d'une pluralité d'éléments de syntaxe est basé sur le remplacement d'éléments de syntaxe dont les valeurs ont une forte probabilité d'occurrence par des éléments de syntaxe dont les valeurs ont une faible probabilité. Le contexte est déterminé pour l'élément syntaxique et la probabilité d'occurrence des valeurs de ces éléments syntaxiques dans le modèle de flux de données qui ont un certain contexte est calculée. Remplacer éléments de syntaxe flux de données ayant un contexte spécifique, si la probabilité d'occurrence calculée de la valeur de l'élément syntaxique est supérieure à un seuil donné, aux éléments syntaxiques dont les valeurs ont une faible probabilité. 3 n. et 10 z.p. f-ly, 4 ill., 2 onglets.

L'invention concerne les technologies de communication et est destinée à mesurer le spectre de signaux acoustiques d'information. EFFET: améliorer la précision de la mesure du spectre des signaux acoustiques d'information, élargir Fonctionnalité dispositifs en liant les valeurs instantanées du spectre à des segments de longueur réglable du signal acoustique temporaire. Pour ce faire, la transformée en cosinus discrète (DCT) est utilisée dans le procédé de mesure du spectre à la place de la transformée de Fourier rapide (FFT), ce qui permet d'augmenter la précision de la mesure du spectre des signaux acoustiques en augmentant la résolution, réduisant le niveau des lobes secondaires de la fenêtre de transformation dans le spectre, et réduisant l'oscillation des composants d'estimation d'amplitude spectrale, et permet également de réduire la durée des segments de signal acoustique sur lesquels le spectre instantané est mesuré, tout en formant deux signaux au lieu d'un (principal et supplémentaire), et le signal acoustique numérique supplémentaire est orthogonal par rapport au principal, les valeurs instantanées mesurées du spectre sont également liées, le module du spectre et la caractéristique phase-fréquence du signal aux segments du signal acoustique temporel réglés par la position temporelle et la durée, sur lesquels ce spectre est mesuré. 2 n.p. f-ly, 8 malades.

L'invention concerne Communication sans fil. Le résultat technique est une augmentation de l'immunité au bruit, de la fiabilité et de l'efficacité de la communication, tandis que la consommation d'énergie peut être réduite. Pour cela, le procédé comprend : une étape S1, dans laquelle le dispositif maître génère un code de séquence au moyen d'un encodeur spécifique, et transmet le code de séquence à chaque dispositif esclave en continu pendant une durée prédéterminée selon une requête de communication, le le codeur étant un registre à décalage de rétroaction exécuté selon un polynôme spécifique, dont l'ordre et les coefficients sont corrélés avec la demande de communication, alors que tous les coefficients et valeurs initiales ne sont pas égaux à 0 en même temps ; Période donnée un temps supérieur ou égal à la somme de la période de sommeil et de la période de détection d'esclave, qui constitue un cycle de sommeil et de réveil ; étape S2, dans laquelle le dispositif esclave reçoit une partie continue du code de séquence dans la période de détection, décode le code de séquence par un décodeur correspondant au codeur, et effectue une opération appropriée selon le résultat de décodage. 2 n. et 10 z.p. f-ly, 5 malades.

L'invention concerne les technologies de communication et est destinée au codage et au décodage de signaux. Le résultat technique est une augmentation de la précision des signaux de codage et de décodage. Le procédé de codage de signal comprend l'obtention d'un signal dans le domaine fréquentiel en fonction d'un signal d'entrée ; attribuer des bits prédéterminés au signal dans le domaine fréquentiel selon une règle d'attribution prédéterminée ; régler l'attribution de bits pour le signal dans le domaine fréquentiel lorsque la fréquence la plus élevée du signal dans le domaine fréquentiel auquel les bits sont attribués dépasse une valeur prédéterminée ; et coder le signal dans le domaine fréquentiel conformément à l'attribution de bits pour le signal dans le domaine fréquentiel. 4 n. et 16 z.p. f-ly, 9 malades.

L'invention concerne le domaine des télécommunications et est destinée à protéger les informations secrètes transmises. Résultat technique - haut niveau sécurité des informations cryptées. Procédé de cryptage d'informations, comprenant la construction d'une table de correspondances de symboles et de leurs équivalents dans l'espace (00 ; FF) dans le système hexadécimal, la génération d'une nouvelle table de correspondances en changeant la table d'origine, en décalant la table d'origine, c'est-à-dire la ligne de correspondances est décalée du nombre de caractères spécifié, le codage de l'information d'origine et sa compression au volume souhaité à l'aide de la table de codage Unicode appropriée. 2 onglet.

L'invention concerne le codage/décodage signal numérique, consistant en blocs consécutifs d'échantillons. Le résultat technique est d'améliorer la qualité du son encodé. Le codage consiste à appliquer une fenêtre de pondération à deux blocs de M échantillons consécutifs. En particulier, une telle fenêtre de pondération est asymétrique et contient quatre sections distinctes, se poursuivant séquentiellement sur les deux blocs mentionnés ci-dessus, tandis que la première section augmente pendant le premier intervalle de temps, la deuxième section a une valeur de pondération constante pendant le deuxième intervalle de temps, la troisième section diminue avec le temps, le troisième intervalle de temps et la quatrième section a une valeur de pondération constante pendant le quatrième intervalle de temps. 6 n. et 11 z.p. f-ly, 10 malades.

L'invention concerne le domaine du traitement numérique du signal, en particulier les procédés de codage/décodage d'images vidéo numériques. Le résultat technique est d'augmenter le taux de compression des images vidéo avec une légère diminution de la qualité de l'image décodée par rapport aux images à caractère haute fréquence du spectre du signal. Un procédé de codage/décodage d'images vidéo numériques est proposé. Selon le procédé, dans le processus de codage, une composante haute fréquence supplémentaire est ajoutée ligne par ligne à la composante basse fréquence de la transformée en ondelettes pour lisser la fonction d'origine, qui est utilisée pour le codage, mais supprimée côté décodage par à l'aide d'un filtre passe-bas. De plus, l'encodage est mis en oeuvre à l'aide d'une fonctionnelle à deux objectifs d'augmentation du taux de compression des données et de maintien de la qualité de l'image décodée, et les caractéristiques du filtre du décodeur sont prises en compte comme une limitation de communication à l'étape d'encodage. 8 ill., 3 onglets.

L'invention concerne le domaine des technologies de communication sans fil. EFFET : amélioration de la qualité de la communication en supprimant les interférences séquentielles entre les flux de signaux. Le procédé de précodage comprend : l'exécution d'un prétraitement de précodage sur un signal à transmettre, le prétraitement provoquant une augmentation de puissance du signal à transmettre ; sélectionner un algorithme de limitation de puissance selon la règle de sélection ; effectuer une opération de limitation de puissance sur le signal prétraité selon l'algorithme de limitation de puissance sélectionné ; et générer un signal précodé selon le signal à puissance limitée. Un mode de réalisation de la présente invention décrit en outre un émetteur, un récepteur et un système de précodage. Dans la présente invention, l'effet néfaste exercé par l'opération de limitation de puissance sur la transmission de signaux peut être réduit autant que possible au moment où la puissance de transmission est limitée en utilisant l'opération de limitation de puissance. 5n. et 12 z.p. f-ly, 8 malades.

La présente invention concerne le domaine du codage et du décodage et est destinée à la quantification de vecteurs d'enveloppe fréquentielle. EFFET : efficacité accrue de la quantification des vecteurs d'enveloppe de fréquence. Le procédé comprend : la division de N enveloppes de fréquence dans une trame en N1 vecteurs, où chaque vecteur dans les N1 vecteurs comprend M enveloppes de fréquence ; quantifier le premier vecteur en N1 vecteurs en utilisant le premier livre de codes pour obtenir un mot de code correspondant au premier vecteur quantifié, ledit premier livre de codes étant divisé en 2B1 sections ; déterminer, selon le mot de code correspondant au premier vecteur quantifié, que le premier vecteur quantifié est associé à la ième section dans les sections 2B1 dudit premier livre de code; déterminer un deuxième livre de codes selon le livre de codes de la ième section ; et quantifier le deuxième vecteur en N1 vecteurs sur la base dudit deuxième livre de codes. Dans des modes de réalisation de la présente invention, les enveloppes de fréquence sont partitionnées en une pluralité de vecteurs plus petits de sorte qu'une quantification vectorielle peut être effectuée sur les vecteurs d'enveloppe de fréquence en utilisant un livre de code avec moins de bits. 2 n. et 6 z.p. f-ly, 3 malades.

Le groupe d'inventions concerne le domaine du codage. Le résultat technique est d'augmenter l'efficacité de la compression des données. Le procédé de codage de données d'entrée (D1) comprend la détermination de blocs de données et/ou de paquets de données essentiellement répétés dans au moins l'un des fragments de données d'entrée (D1), tandis que les blocs de données et/ou les paquets de données comprennent un ensemble correspondant d'éléments, où les éléments comprennent un ensemble de bits déterminer si des éléments sont inchangés dans des blocs de données et/ou des paquets de données sensiblement répétés, et/ou déterminer si des éléments dans des blocs de données et/ou des paquets de données sensiblement répétés changent ; coder les éléments inchangés en données codées (E2) en utilisant au moins un symbole correspondant ou au moins un bit correspondant indiquant aucun changement dans les éléments inchangés par rapport à leurs éléments correspondants dans le bloc de données de référence et/ou le paquet de données ; et coder les éléments modifiés en données codées (E2). 6 n. et 28 z.p. f-ly, 8 malades.

L'invention concerne les décodeurs. Le résultat technique consiste à augmenter la vitesse des dispositifs de conversion d'informations utilisant le décodeur de l'invention. La première entrée logique du dispositif est reliée à l'entrée du troisième miroir de courant, la deuxième entrée logique du dispositif est reliée à l'entrée du premier miroir de courant, la première sortie courant du premier miroir de courant est reliée au combiné émetteurs des deuxième et cinquième transistors de sortie et est connectée au deuxième bus d'alimentation par l'intermédiaire d'une source de courant de référence auxiliaire, la deuxième sortie de courant du premier miroir de courant est connectée aux émetteurs combinés des premier et quatrième transistors de sortie et est connectée à la première sortie de courant du troisième miroir de courant, le collecteur du second transistor de sortie est connecté à l'entrée du second miroir de courant dont la sortie de courant est connectée aux émetteurs combinés des troisième et sixième transistors de sortie et est connectée à la deuxième sortie de courant du troisième miroir de courant, et le collecteur du cinquième transistor de sortie est connecté au deuxième bus d'alimentation. 3 sem. f-ly, 5 malades.

Les décodeurs sont des dispositifs fonctionnels numériques conçus pour reconnaître les codes binaires.

Les décodeurs binaires, étant un convertisseur de code, convertissent un code binaire à usage direct en un code "1 sur N". Dans une telle combinaison de codes, un seul bit est occupé par une unité, et tous les autres sont nuls. La table de vérité d'un décodeur conçu pour reconnaître un code binaire à quatre bits est présentée dans le tableau. 2.1

Tableau 2.1

Le tableau 1 montre que, selon le code binaire d'entrée, une seule de ses sorties est à l'état excité en sortie du décodeur. Il résulte du même tableau qu'un décodeur binaire à n entrées doit avoir 2 n sorties correspondant au nombre de combinaisons de codes d'un code binaire à n bits. Un tel décodeur est appelé Achevée

, Contrairement à incomplet

, pour laquelle une partie des combinaisons de codes d'entrée n'est pas utilisée, et le nombre de sorties pour lesquelles  moins de 2n.

moins de 2n.

Dans le champ principal du symbole du décodeur (Fig. 2.5), les lettres DC (du mot anglais Decoder) sont apposées. Les entrées du décodeur sont généralement désignées par leurs poids binaires. En plus des entrées d'informations, le décodeur possède généralement une ou plusieurs entrées de validation de travail, notées E (Activer). S'il y a un signal de validation sur cette entrée, le décodeur fonctionne conformément à la table de vérité, en son absence, toutes les sorties du décodeur sont passives.

Le fonctionnement du décodeur est décrit par un système d'expressions booléennes :

DE  la solution chimiotechnique des décodeurs est représentée sur la Fig. 2.6.

la solution chimiotechnique des décodeurs est représentée sur la Fig. 2.6.

Comme on peut le voir sur la fig. 2.6., le décodeur se compose de 2n inverseurs du code d'entrée, qui forment les valeurs directes et inverses des variables de code d'entrée, de deux inverseurs à l'entrée d'autorisation et de 2 n -1 conjoncteurs, qui forment les sorties du circuit . La faible capacité binaire des décodeurs série pose la question de l'augmentation de leur capacité binaire. A partir de décodeurs low-bit, vous pouvez construire un circuit équivalent à un décodeur large-bit. A cet effet, le mot d'entrée est divisé en champs, tandis que la profondeur en bits du champ des chiffres les moins significatifs correspond à la largeur en bits des décodeurs disponibles. Le champ restant des bits les plus significatifs est utilisé pour obtenir un signal permettant le fonctionnement de l'un des décodeurs qui décodent le champ des bits les moins significatifs.

À  à titre d'exemple sur la Fig. 2.7 montre un schéma de décodage d'un code à cinq bits à l'aide des décodeurs "3-8" et "2-4". Pour obtenir les 32 sorties requises, une colonne du deuxième étage est compilée à partir de quatre décodeurs "3-8" DC1-DC4. Le décodeur "2-4" prend les deux bits les plus significatifs du code d'entrée. La sortie excitée de ce décodeur ouvre l'un des décodeurs de colonne à l'entrée de validation, et le décodeur sélectionné décode les bits les moins significatifs du mot d'entrée. Chaque mot d'entrée correspond à l'excitation d'une des sorties F 0 -F 31 . Par exemple, lors du décodage du mot x 4 x 3 x 2 x 1 x 0 =11001 2 =25 10, l'entrée du décodeur de premier niveau a le code 11, qui excite sa sortie numéro trois (marquée d'une croix), ce qui permet le fonctionnement du décodeur DC4. L'entrée DC4 est codée 001, donc sa première sortie sera alimentée, c'est-à-dire Sortie 25 circuits. L'autorisation ou l'interdiction générale de fonctionnement du circuit s'effectue à l'entrée E du décodeur du premier étage.

à titre d'exemple sur la Fig. 2.7 montre un schéma de décodage d'un code à cinq bits à l'aide des décodeurs "3-8" et "2-4". Pour obtenir les 32 sorties requises, une colonne du deuxième étage est compilée à partir de quatre décodeurs "3-8" DC1-DC4. Le décodeur "2-4" prend les deux bits les plus significatifs du code d'entrée. La sortie excitée de ce décodeur ouvre l'un des décodeurs de colonne à l'entrée de validation, et le décodeur sélectionné décode les bits les moins significatifs du mot d'entrée. Chaque mot d'entrée correspond à l'excitation d'une des sorties F 0 -F 31 . Par exemple, lors du décodage du mot x 4 x 3 x 2 x 1 x 0 =11001 2 =25 10, l'entrée du décodeur de premier niveau a le code 11, qui excite sa sortie numéro trois (marquée d'une croix), ce qui permet le fonctionnement du décodeur DC4. L'entrée DC4 est codée 001, donc sa première sortie sera alimentée, c'est-à-dire Sortie 25 circuits. L'autorisation ou l'interdiction générale de fonctionnement du circuit s'effectue à l'entrée E du décodeur du premier étage.

Parallèlement à l'utilisation des décodeurs pour leur destination, ils peuvent être utilisés pour implémenter des fonctions logiques arbitraires, puisque tous les termes conjonctifs qui peuvent être composés à partir d'un nombre donné d'arguments sont générés aux sorties du décodeur. Une fonction logique dans SDNF est une disjonction d'un certain nombre de ces termes. En les combinant selon le schéma OU, vous pouvez obtenir n'importe quelle fonction d'un nombre donné d'arguments.

La figure 2.8 montre l'implémentation matérielle de la fonction d'additionneur modulo deux à titre d'exemple.

Un des éléments très importants technologie digitale, et en particulier dans les ordinateurs et les systèmes de contrôle sont des encodeurs et des décodeurs.

Lorsque nous entendons le mot encodeur ou décodeur, des phrases de films d'espionnage nous viennent à l'esprit. Quelque chose comme : déchiffrer la dépêche et chiffrer la réponse.

Il n'y a rien de mal à cela, puisque les machines de cryptage de nos résidences et des résidences étrangères utilisent des encodeurs et des décodeurs.

Encodeurs.

Ainsi, l'encodeur (encodeur) est appareil électronique, dans ce cas, un microcircuit qui convertit le code d'un système numérique en code d'un autre système. Les plus utilisés en électronique sont les codeurs qui convertissent un code décimal positionnel en binaire parallèle. C'est ainsi que le codeur peut être indiqué sur le schéma de circuit.

Par exemple, imaginons que nous tenons dans nos mains une calculatrice ordinaire, qui est maintenant utilisée par n'importe quel étudiant.

Étant donné que toutes les actions de la calculatrice sont effectuées avec des nombres binaires (rappelez-vous les bases de l'électronique numérique), il y a un encodeur après le clavier qui convertit les nombres saisis en forme binaire.

Tous les boutons de la calculatrice sont reliés à un fil commun et, en appuyant par exemple sur le bouton 5 à l'entrée de l'encodeur, on obtient immédiatement la forme binaire de ce nombre à sa sortie.

Bien sûr, l'encodeur de la calculatrice a Suite entrées, car en plus des nombres, vous devez y entrer quelques symboles supplémentaires d'opérations arithmétiques, par conséquent, non seulement les nombres sous forme binaire, mais également les commandes sont supprimées des sorties de l'encodeur.

Si l'on considère la structure interne du codeur, il est facile de s'assurer qu'il est réalisé sur les éléments logiques de base les plus simples.

Dans tous les dispositifs de commande fonctionnant sur une logique binaire, mais pour la commodité de l'opérateur, un clavier décimal utilise des encodeurs.

Décodeurs.

Les décodeurs appartiennent au même groupe, sauf qu'ils fonctionnent exactement à l'opposé. Ils convertissent le binaire parallèle en décimal positionnel. La désignation graphique conditionnelle sur le diagramme peut être la suivante.

Ou comme ça.

En parlant plus en détail des décodeurs, il convient de dire qu'ils peuvent convertir le code binaire en différents systèmes calcul (décimal, hexadécimal, etc.). Tout dépend du but spécifique et du but du microcircuit.

L'exemple le plus simple. Vous avez vu plus d'une fois un indicateur numérique à sept segments, par exemple une LED. Il affiche les chiffres décimaux et les nombres auxquels nous sommes habitués depuis l'enfance (1, 2, 3, 4...). Mais, comme vous le savez, l'électronique numérique fonctionne avec des nombres binaires, qui sont une combinaison de 0 et 1. Qu'est-ce qui a converti le code binaire en décimal et soumis le résultat à un indicateur numérique à sept segments ? Vous avez probablement déjà deviné que le décodeur l'a fait.

Le travail du décodeur peut être évalué en direct si vous assemblez un circuit simple composé d'une puce de décodeur K176ID2 et un indicateur LED à sept segments, également appelé "huit". Regardez le schéma, il est plus facile de comprendre le fonctionnement du décodeur. Une planche à pain sans soudure peut être utilisée pour assembler rapidement le circuit.

Pour référence. Le microcircuit K176ID2 a été développé pour contrôler un indicateur LED à 7 segments. Cette puce est capable de convertir le code binaire de 0000 avant de 1001 , qui correspond aux chiffres décimaux de 0 à 9 (une décade). Les autres combinaisons plus anciennes ne sont tout simplement pas affichées. Les conclusions C, S, K sont auxiliaires.

La puce K176ID2 possède quatre entrées (1, 2, 4, 8). Ils sont parfois aussi appelés D0-D3. Ces entrées reçoivent un code binaire parallèle (par exemple, 0001). Dans ce cas, le code binaire a 4 bits. Le microcircuit convertit le code pour que les sorties ( a-g) apparaissent des signaux qui forment des chiffres décimaux et des nombres auxquels nous sommes habitués sur l'indicateur à sept segments. Étant donné que le décodeur K176ID2 est capable d'afficher des chiffres décimaux dans la plage de 0 à 9, nous ne les verrons que sur l'indicateur.

4 interrupteurs à bascule (S1 - S4) sont connectés aux entrées du décodeur K176ID2, à l'aide desquels un code binaire parallèle peut être appliqué au décodeur. Par exemple, lors de la fermeture de l'interrupteur à bascule S1 une unité logique est appliquée à la 5ème sortie du microcircuit. Si vous ouvrez les contacts de l'interrupteur à bascule S1- cela correspondra à un zéro logique. À l'aide d'interrupteurs à bascule, nous pouvons régler manuellement la logique 1 ou 0 aux entrées du microcircuit.Je pense que tout est clair avec cela.

Le schéma montre comment le code 0101 est appliqué aux entrées du décodeur DD1. Indicateur LED le chiffre 5 s'affichera. Si seul l'interrupteur à bascule S4 est fermé, alors le chiffre 8 s'affichera sur l'indicateur. Pour écrire un nombre de 0 à 9 en code binaire, quatre chiffres suffisent : un 3 * 8 + un 2 * 4 + un 1 * 2 + un 0 * 1, où un 0 - un 3, sont des nombres du système numérique (0 ou 1).

Représentons le nombre 0101 sous forme décimale 0101 = 0*8 + 1*4 + 0*2 + 1*1 = 4 + 1 = 5 . Regardons maintenant le diagramme et voyons que le poids du chiffre correspond au nombre multiplié par 0 ou 1 dans la formule.

Un décodeur basé sur la technologie TTL - K155ID1 a été utilisé à un moment donné pour contrôler un indicateur numérique à décharge de type IN8, IN12, très demandé dans les années 70, car les indicateurs LED basse tension étaient encore très rares.

Tout a changé dans les années 80. Il était possible d'acheter librement des matrices LED à sept segments (indicateurs) et un boom dans l'assemblage d'horloges électroniques balayé parmi les radioamateurs. Fait maison Montre numérique pas collecté pour la maison seulement paresseux.

Comme indiqué au paragraphe 3.2, les appareils numériques sont divisés en combinés et séquentiels. Les dispositifs combinés comprennent de tels dispositifs numériques, dont les signaux de sortie ne dépendent que de la valeur actuelle des signaux d'entrée. Ces dispositifs, contrairement aux dispositifs séquentiels, n'ont pas de mémoire. Une fois les processus transitoires terminés dans ces appareils, les valeurs de sortie sont définies à leurs sorties, qui ne sont pas affectées par la nature des processus transitoires.

Tout complexe appareil numérique peut être divisé en une partie combinatoire qui effectue des opérations logiques et des éléments de mémoire. En principe, la partie combinatoire peut être réalisée sur des éléments logiques, mais cela est trop compliqué et coûteux. Il est beaucoup plus facile d'utiliser des dispositifs combinatoires prêts à l'emploi pour cela. Les principaux dispositifs combinatoires comprennent les décodeurs, les codeurs, les multiplexeurs (distributeurs), les démultiplexeurs et les additionneurs.

Décodeurs

Décodeur (décodeur ) – Il s'agit d'un appareil combinatoire qui vous permet de reconnaître les nombres représentés par un code positionnel à n bits. Si à l'entrée du décodeur "-bit code binaire, alors à sa sortie le code "1 de Ν". Dans la combinaison de codes de ce code, une seule position est occupée par une, et toutes les autres sont nulles. Par exemple, le code "1 de Ν", contenant 4 combinaisons de codes sera représenté comme suit :

Un tel code s'appelle unitaire par conséquent, le décodeur est un convertisseur d'un code binaire positionnel en un code unitaire. Puisque le nombre possible de nombres codés par un code binaire à n bits est égal au nombre d'ensembles de et d'arguments (N = 2"), alors un décodeur à n entrées doit avoir 2n sorties. Un tel décodeur est dit complet. Si une partie des ensembles d'entrées n'est pas utilisée, alors le décodeur est dit incomplet, et son nombre de sorties est inférieur à 2n. Ainsi, selon le code binaire d'entrée, un seul des circuits de sortie est excité en sortie du décodeur, au nombre duquel le numéro d'entrée peut être reconnu.

Les décodeurs sont utilisés pour déchiffrer les adresses des cellules de mémoire, afficher des lettres et des chiffres sur des moniteurs, des indicateurs et d'autres appareils. Le plus souvent, ils sont intégrés dans le LSI, comme par exemple dans les dispositifs de mémoire à semi-conducteurs, mais ils sont également disponibles en tant que circuits intégrés du niveau d'intégration intermédiaire.

Illustrons la mise en oeuvre de décodeurs à l'aide de l'exemple d'un décodeur complet de nombres à trois chiffres. La table de vérité du décodeur est présentée dans le tableau. 3.5.

Tableau 3.5

|

X 3 |

X 2 |

X 1 |

y 0 |

y 1 |

y 2 |

y 3 |

y 4 |

y 5 |

y 6 |

y 7 |

|

Comme vous pouvez le voir, chaque sortie X i est égal à un sur un seul ensemble, donc le fonctionnement du décodeur est décrit par huit fonctions - selon le nombre de sorties du décodeur, dont chacune est une conjonction (ET logique) de trois arguments :

Le schéma d'un décodeur complet à trois bits est illustré à la fig. 3.12. Pour implémenter une fonction y i, un connecteur à trois entrées est nécessaire. Puisqu'il existe à la fois des arguments directs et inverses aux entrées des conjoncteurs, trois inverseurs sont nécessaires dans le circuit décodeur (voir Fig. 3.12, un).

Riz. 3.12.

un – schéma logique; b – symbole du décodeur avec entrées de synchronisation et de résolution

Souvent, les décodeurs sont réalisés avec une synchronisation contrôlée, dans laquelle le décryptage du code sera effectué lors de la fourniture de l'impulsion d'horloge reçue en entrée DE, uniquement à condition que l'entrée FR un signal unique permissif a été donné (voir Fig. 3.12, b). Pour mettre en oeuvre une telle condition, il faut des connecteurs à quatre entrées dont la quatrième entrée reçoit un signal de validation. Ce signal est généré par un connecteur à deux entrées lorsque les signaux correspondent DE et FR.

Le nombre de contacts dans un boîtier standard d'un CI simple est limité (14, 16 ou 24), de sorte que les décodeurs produits sous la forme d'un CI ont une petite taille de code d'entrée (trois, moins souvent quatre). Ainsi, par exemple, seul un décodeur complet à trois bits peut être placé dans un boîtier à 16 broches. S'il est nécessaire de créer un décodeur d'une plus grande capacité, une connexion en cascade de décodeurs d'une petite capacité est utilisée.

Exemple 3.1. Soit nécessaire de créer un décodeur à cinq bits basé sur des décodeurs à trois bits (Fig. 3.13).

Riz. 3.13.

La solution. Un décodeur à cinq bits devrait avoir 25 = 32 sorties. Divisez les cinq chiffres en chiffres juniors X 2, X 1, X 0 et plus X 4, X 3. Ensuite, les plus jeunes peuvent être appliqués aux entrées de quatre décodeurs 3 bits du deuxième étage et former 8 4 = 32 sorties. Utilisation des entrées d'activation ΕΝ, vous pouvez choisir l'un des quatre décodeurs du deuxième étage, qui doit former un seul signal. Pour ce faire, nous allons fournir les deux bits supérieurs aux entrées du décodeur de contrôle du premier étage, et connecter ses sorties aux entrées de validation ΕΝ décodeurs du premier étage.

Soit, par exemple, le code d'entrée égal à 11011 = 2710. Les bits de poids fort étant "11", le décodeur de commande permettra le fonctionnement du 4ème décodeur du deuxième étage. Dans ce cas, les sorties des trois premiers décodeurs seront des zéros, et la sortie "3" du quatrième décodeur, c'est-à-dire F 27 sera logique.

Les décodeurs sont largement utilisés dans les systèmes de contrôle procédés technologiques. De nombreux actionneurs, tels qu'un moteur électrique, un actionneur à base d'électroaimant, peuvent être contrôlés avec seulement deux commandes : "on" et "off". Dans ce cas, il convient d'affecter un "1" logique à la commande "on", et un "1" logique à la commande "off". Pour contrôler de tels appareils, des codes unitaires sont utilisés, dans lesquels chaque chiffre est associé de manière rigide à appareil spécifique. Le nombre d'appareils contrôlés peut être de plusieurs dizaines et le décodeur doit avoir un nombre approprié de sorties.

Sur la fig. 3.14 montre un schéma de commande pour huit actionneurs basé sur un décodeur. Le circuit contient huit circuits similaires qui activent / désactivent l'actionneur. L'état du dispositif exécutif est fixé par un élément de mémoire, qui est le plus souvent utilisé comme déclencheur (voir paragraphe 3.9). L'entrée du haut active l'élément et celle du bas l'éteint. Le signal qui détermine l'état activé ou désactivé est envoyé aux circuits ET correspondants (supérieurs ou inférieurs) de tous les éléments de mémoire, mais ce signal n'est perçu que par l'élément sélectionné par le décodeur. Pour ce faire, en plus des signaux ON/OFF, le circuit de commande reçoit simultanément un code qui entre dans le décodeur et détermine le numéro de l'actionneur. Le signal provenant de la sortie de l'élément de mémoire est amplifié et entre dans le circuit de commutation de l'actionneur. Ici, il est possible d'installer un optocoupleur à isolation galvanique (voir paragraphe 2.10), un relais électromagnétique qui fournit une haute tension de commutation, par exemple = 220 V, un démarreur électromagnétique qui fournit une tension triphasée au moteur électrique.

Riz. 3.14.

Encodeurs

encodeur – il s'agit d'un dispositif combinatoire qui exécute les fonctions inverses du décodeur. Lorsqu'un signal est appliqué sur l'une de ses entrées (code unitaire), le code binaire correspondant doit être formé en sortie.

Si le nombre d'entrées du codeur est 2n, alors le nombre de sorties doit évidemment être égal à P, ceux. le nombre de bits binaires pouvant coder des situations de 2".

Illustrons la synthèse du circuit codeur pour P = 3. La table de vérité a la forme indiquée dans le tableau. 3.6.

Tableau 3.6

|

X |

X |

||||||

|

y 3 |

y 2 |

y 1 |

y 3 |

y 2 |

y 1 |

||

Le fonctionnement du codeur est décrit par trois fonctions à 3, y 2,y 1, dont chacun est égal à un sur quatre ensembles (le numéro d'ensemble correspond au numéro d'entrée). Les sovDNF des fonctions de sortie sont :

Trois fonctions sont mises en œuvre par trois disjoncteurs (Fig. 3.15), aux sorties desquels un code binaire à trois bits est formé.

Riz. 3.15.

En même temps, l'argument X 0 n'est inclus dans aucune des fonctions logiques et le bus X 0 est laissé inutilisé. En effet, le signal d'entrée x0 doit correspondre au code « 000 », qui sera toujours en sortie du codeur si tous les autres arguments sont nuls.

En plus des codeurs conventionnels, il existe également encodeurs prioritaires. De tels codeurs effectuent une opération plus complexe. Pendant le fonctionnement des ordinateurs et autres appareils, le problème de la détermination d'un concurrent prioritaire pour le service est souvent résolu. Plusieurs concurrents soumettent leurs demandes de service qui ne peuvent être satisfaites en même temps. Vous devez choisir qui bénéficie du service prioritaire. La version la plus simple du problème consiste à attribuer une priorité fixe à chaque source de requêtes. Par exemple, un groupe de huit demandes R 7, ..., R 0 (R - de l'anglais. demande – demande) est formé de manière à ce que la source numéro sept ait la priorité la plus élevée, puis la priorité diminue de numéro en numéro. La source de la puce a la priorité la plus basse - elle ne sera servie que si toutes les autres demandes sont absentes. S'il y a plusieurs demandes en même temps, la demande avec le plus grand nombre est servie.

L'encodeur de priorité délivre le nombre binaire de la requête la plus élevée. Avec une seule entrée excitée, le codeur prioritaire fonctionne de la même manière que le codeur binaire. Par conséquent, dans la série IC, un codeur binaire en tant qu'élément indépendant peut être absent. Son mode de fonctionnement est un cas particulier du codeur prioritaire.

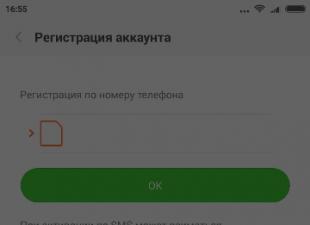

sushiandbox.ru Mastering PC - Internet. Skype. Réseaux sociaux. Cours sur Windows.

sushiandbox.ru Mastering PC - Internet. Skype. Réseaux sociaux. Cours sur Windows.